# LED Driver, 12-channel, Constant Current

The LC75760UJA is 12-channel LED driver having shift register circuit (serial input, series/parallel output), latch circuit, LED driver of the constant current output type. It is usable for display such as illumination, the backlight LED, the warning light of the instrument panel. This LSI has 6-ch PWM (Pulse Width Modulation) function to perform brightness adjustment of the LED. Furthermore, built-in the thermal protection function and open/short/adjacent outputs short detection function.

#### **Features**

- The LED Driver Outputs of Up to 12-ch can Drive LED Directly

- ◆ Constant Current Output Form

- ◆ Output Voltage: Absolute Maximum Rating Maximum Operating Voltage

◆ Output Current: Absolute Maximum Rating Maximum Operating Current

50 mA

- Output Current Regulation Function (256 Steps)

- Open/Short/Adjacent Outputs Short Detection Function

- Slew Rate Limited Switching Function

- Serial Data Communication Supports 4-line Serial Format

- Support 3.3 V and 5.0 V Operation

- Maximum Operating Frequency 2 MHz

- Built-in 6-ch PWM Function for Brightness Adjustment of LED

- Resolution of 128, 256, 512 or 1024 Steps

- PWM Frame Frequency can be Controlled by Serial Data

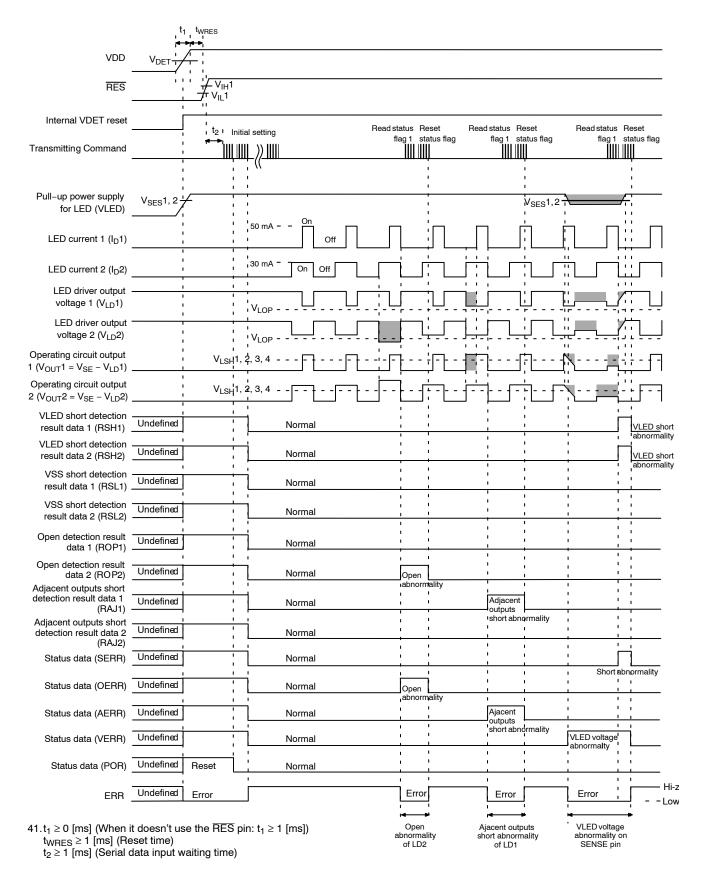

- Built-in Thermal Protection Function (125°C: Automatic Adjustment of PWM, 150°C: Forced-off All LEDs)

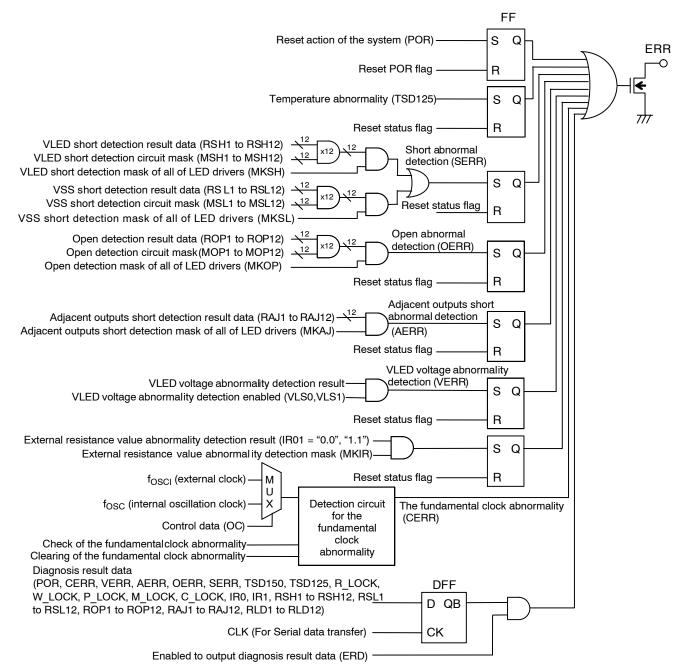

- Provides the ERR Output Pin (125°C Temperature Abnormality, Open/Short/Adjacent Outputs Short Abnormality, LED Pull-up Supply Voltage Abnormality, External Resistance Abnormally, Fundamental Clock Abnormality, Reset Action)

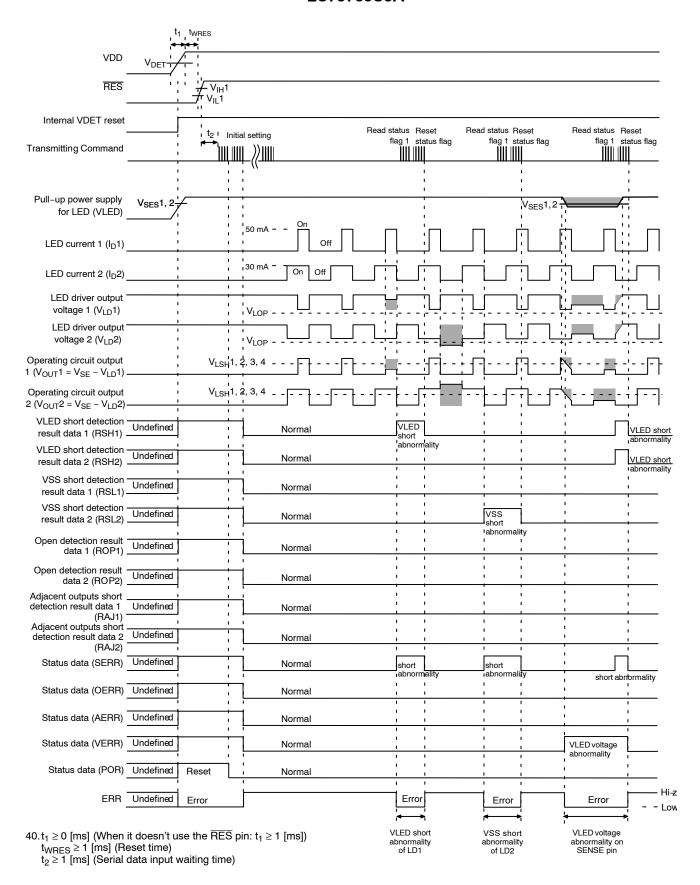

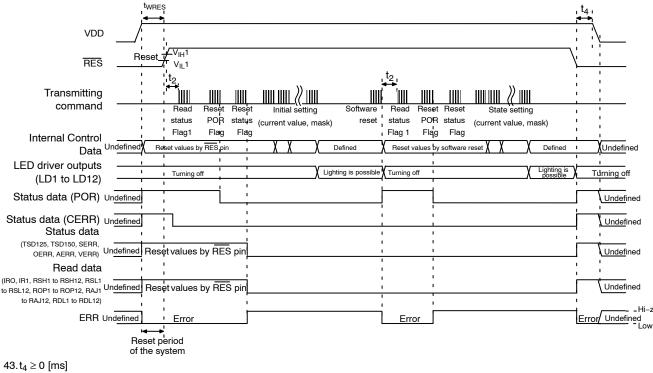

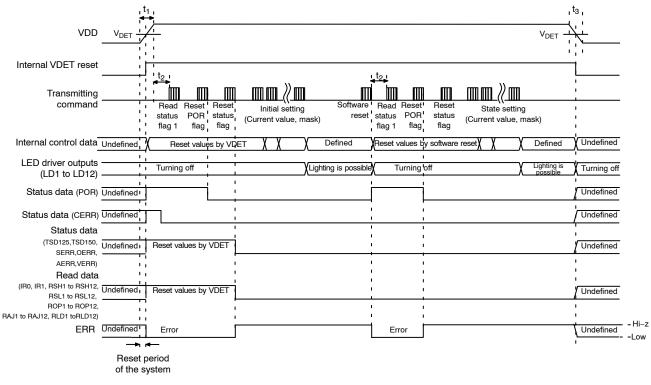

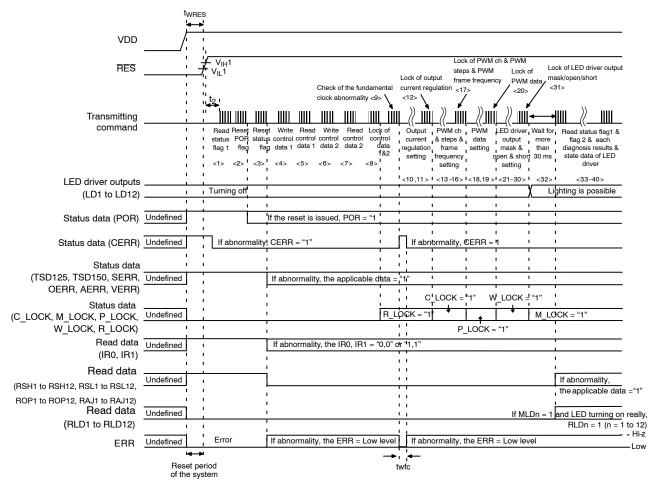

- Provides a RES Pin and Built-in Voltage Detection Type Reset Circuit (VDET) for LSI Internal Initialization

- Switch of the Internal Oscillator Operating Mode and the External Clock Operating Mode can be Controlled by Serial Data

- Built-in Oscillator Circuit. (Built-in Resister and Capacitor for Oscillation)

- Built-in External Resistance Value Diagnosis Function for Constant Current

- AEC-Q100 Qualified and PPAP Capable

#### **Typical Applications**

- Automotive: Instrument Cluster, HVAC, Head Up Display

- Industrial: Measurement Equipment

#### ON Semiconductor®

www.onsemi.com

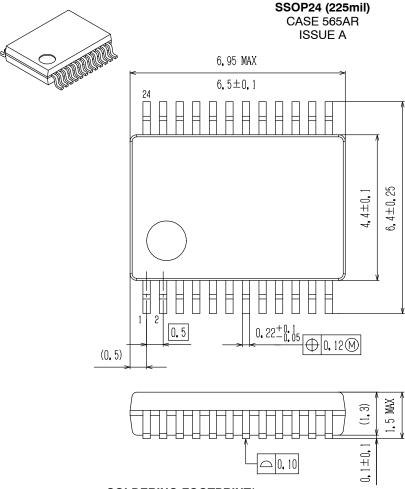

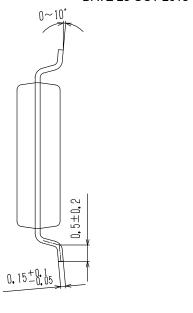

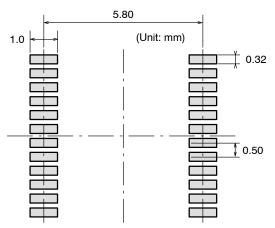

SSOP24 (225 mil) CASE 565AR

#### **MARKING DIAGRAM**

XXXXX = Specific Device Code Y = Year M = Month DDD = Additional Traceability Data

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 63 of this data sheet.

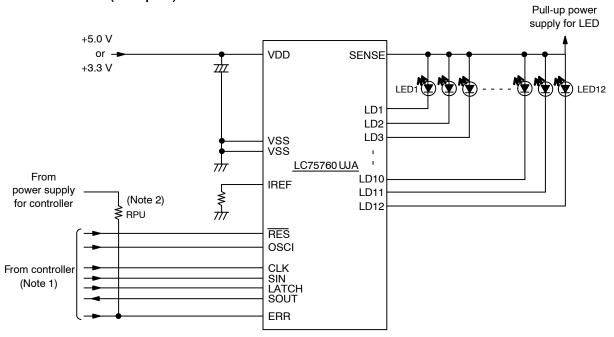

#### (Example 1) One LC75760UJA is used with 4-line serial interface format.

- 1. The pins to be connected to the controller (CLK, SIN, LATCH, RES, OSCI) can handle 3.3 V or 5 V.

- 2. The ERR pin with an open-drain output type requires a pull-up resistor (RPU). Select a resistance (between 1 k $\Omega$  and 10 k $\Omega$ ) appropriate for the capacitance of the external wiring so that signal waveforms are not degraded.

Figure 1. Application Schematic 1

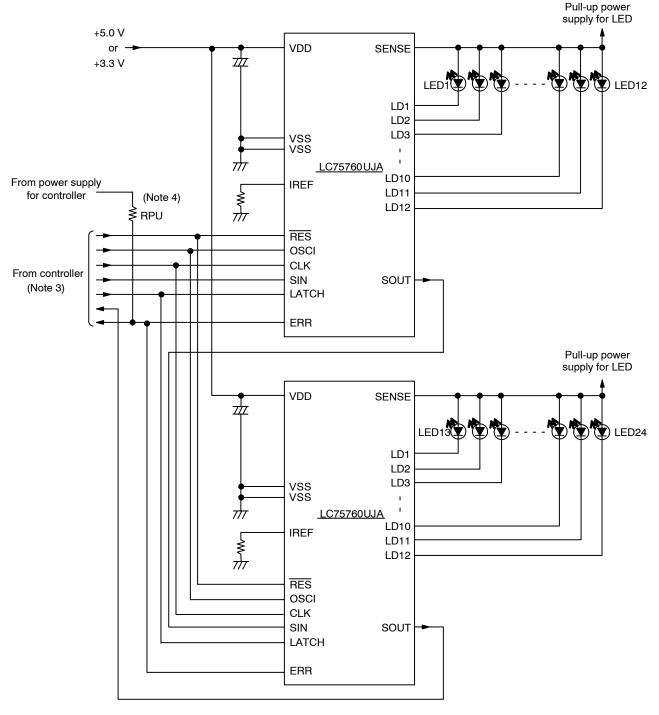

(Example 2) Two LC75760UJA are used with 4-line serial interface format.

- 3. The pins to be connected to the controller (CLK, SIN, LATCH,  $\overline{\text{RES}}$ , OSCI) can handle 3.3 V or 5 V.

- 4. The ERR pin with an open-drain output type requires a pull-up resistor (RPU). Select a resistance (between 1 k $\Omega$  and 10 k $\Omega$ ) appropriate for the capacitance of the external wiring so that signal waveforms are not degraded.

Figure 2. Application Schematic 2

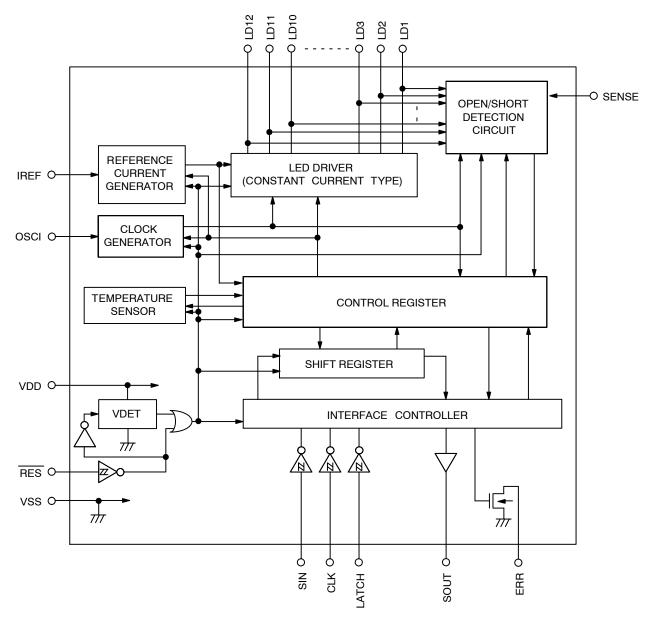

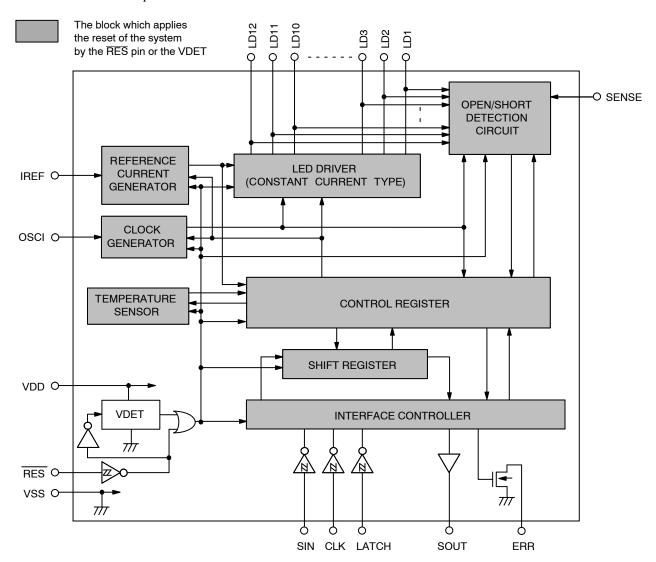

#### **BLOCK DIAGRAM**

Figure 3. Simplified Block Diagram

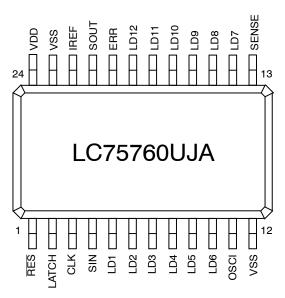

#### **PIN ASSIGNMENT**

Figure 4. Pin Assignment (Top View)

#### **PIN FUNCTION**

| Pin Name                   | Pin No.              | Function                                                                                                                                                                                                                                                                                                                                                 | Active | I/O | Handing<br>when<br>Unused |

|----------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|---------------------------|

| VDD                        | 24                   | This is power supply pin. Supply the voltage between +2.7 V and +5.5 V.                                                                                                                                                                                                                                                                                  | -      | -   | -                         |

| VSS                        | 12, 23               | These are power supply pins. Connect to GND.                                                                                                                                                                                                                                                                                                             | -      | -   | -                         |

| SIN                        | 4                    | This is an input pin for serial data transfer, and connects to the controller. Input the serial data. The serial data are received at the rising edge of the shift clock (CLK).                                                                                                                                                                          | -      | I   | GND                       |

| CLK                        | 3                    | This is an input pin for serial data transfer, and connects to the controller. Input the shift clock.                                                                                                                                                                                                                                                    |        | I   | GND                       |

| LATCH                      | 2                    | This is an input pin for serial data transfer, and connects to the controller. Input the latch pulse.                                                                                                                                                                                                                                                    | Н      | I   | GND                       |

| OSCI                       | 11                   | This is an input pin for the external clock. Input the clock (f <sub>OSCI</sub> 1 = 200 kHz or f <sub>OSCI</sub> 2 = 150 kHz) from the external, when it is the external clock operating mode. Connect to GND, when it is the internal oscillator operating mode.                                                                                        | -      | I   | GND                       |

| RES                        | 1                    | This is an input pin for reset.  - RES = Low(VSS): Reset(Initialization of LSI internal) Refer to "About the reset of the system" for the elaboration.  - RES = High(VDD): Normal operation                                                                                                                                                              | L      | ı   | VDD                       |

| LD1 to LD6,<br>LD7 to LD12 | 5 to 10,<br>14 to 19 | These are LED driver output pins. These output pins are constant current output. Brightness control of the LED is possible by the output current regulation function and the PWM function. When there are LED driver output pins not to use, set mask control data (MLD1 to MLD12) of the corresponding LED driver output pins to "0" (LED turning off). | -      | 0   | OPEN                      |

#### PIN FUNCTION (continued)

| Pin Name | Pin No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Active | I/O | Handing<br>when<br>Unused |

|----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|---------------------------|

| SENSE    | 13      | This is a pull-up voltage monitor pin for LED. Input pull-up power supply voltage (6.3 V max) for LED.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -      | I   | -                         |

| IREF     | 22      | This is a resistance connection pin for reference current (IREF) setting. Connect resistance between IREF pin and GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -      | I   | -                         |

| ERR      | 20      | This is error detection signal output pin (open drain output). When temperature abnormality (TSD125 = "1") or short abnormality of over one LED driver output (SERR = "1") or open abnormality of over one LED driver output (OERR = "1") or adjacent outputs short abnormality of over one LED driver output (AERR = "1") or LED driver supply voltage abnormality (VERR = "1") or the external resistance value abnormality (IR1,0 = "0,0", "1,1") or fundamental clock abnormality (CERR = "1") or reset action (POR = "1") of the system occurred, the ERR pin outputs Low (VSS). Furthermore, connect the external pull-up resistor.  In addition, if the control data ERD is "1", application can read each diagnosis result data from the ERR pin with serial data transfer clock. | -      | 0   | OPEN                      |

| SOUT     | 21      | This is a serial data output pin for shift registers (CMOS output). This pin outputs data from a falling edge of shift clock (CLK).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -      | 0   | OPEN                      |

#### **MAXIMUM RATINGS** $(V_{SS} = 0 V)$

| Symbol              | Parameter                   | Conditions                                | Ratings                      | Unit |

|---------------------|-----------------------------|-------------------------------------------|------------------------------|------|

| V <sub>DD</sub> max | Maximum Supply Voltage      | VDD                                       | -0.3 to +6.5                 | V    |

| V <sub>IN</sub> 1   | Input Voltage               | SIN, CLK, LATCH, RES, OSCI                | -0.3 to +6.5                 | V    |

| V <sub>IN</sub> 2   |                             | IREF                                      | -0.3 to V <sub>DD</sub> +0.3 |      |

| V <sub>IN</sub> 3   |                             | SENSE                                     | -0.3 to +6.8                 |      |

| V <sub>OUT</sub> 1  | Output Voltage              | ERR                                       | -0.3 to +6.5                 | ٧    |

| V <sub>OUT</sub> 2  |                             | SOUT                                      | -0.3 to V <sub>DD</sub> +0.3 |      |

| V <sub>OUT</sub> 3  |                             | LD1 to LD12                               | -0.3 to +6.8                 |      |

| I <sub>OUT</sub> 1  | Output Current              | SOUT, ERR                                 | 10                           | mA   |

| I <sub>OUT</sub> 2  |                             | LD1 to LD12                               | 60                           |      |

| P <sub>dmax</sub> 1 | Allowable Power Dissipation | $T_A = +25^{\circ}C$ with PCB (Note 5)    | 1200                         | mW   |

| P <sub>dmax</sub> 2 |                             | $T_A = +95^{\circ}C$ with PCB (Note 5)    | 525                          |      |

| P <sub>dmax</sub> 3 |                             | $T_A = +105$ °C with PCB (Note 5)         | 430                          |      |

| P <sub>dmax</sub> 4 |                             | $T_A = +25^{\circ}C$ with PCB (Note 6)    | 2000                         |      |

| P <sub>dmax</sub> 5 |                             | $T_A = +95^{\circ}C$ with PCB (Note 6)    | 880                          |      |

| P <sub>dmax</sub> 6 |                             | T <sub>A</sub> = +105°C with PCB (Note 6) | 720                          |      |

| T <sub>J</sub> max  | Junction Temperature        |                                           | +150                         | °C   |

| T <sub>opr</sub>    | Operating Temperature       |                                           | -40 to +105                  | °C   |

| T <sub>stg</sub>    | Storage Temperature         |                                           | -55 to +150                  | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

<sup>5.</sup> The PCB is a glass-epoxy board of 76.2 mm × 114.3 mm × 1.6 mm with 2 layers.

6. The PCB is a glass-epoxy board of 76.2 mm × 114.3 mm × 1.6 mm with 4 layers.

#### **RECOMMENDED OPERATING RANGES** ( $V_{SS} = 0 \text{ V}, T_A = -40 \text{ to } +105^{\circ}\text{C}$ )

| Symbol              | Parameter                      | Conditions                                         | Min                  | Тур | Max                 | Unit |

|---------------------|--------------------------------|----------------------------------------------------|----------------------|-----|---------------------|------|

| V <sub>DD</sub>     | Supply Voltage                 | VDD                                                | 2.7                  | =   | 5.5                 | V    |

| V <sub>IH</sub> 1   | Input High-level Voltage       | SIN, CLK, LATCH, RES, OSCI<br>VDD = 3.6 V to 5.5 V | 0.45 V <sub>DD</sub> | -   | 5.5                 | V    |

|                     |                                | SIN, CLK, LATCH, RES, OSCI<br>VDD = 2.7 V to 3.6 V | 0.6 V <sub>DD</sub>  | -   | 3.6                 |      |

| V <sub>IL</sub> 1   | Input Low-level Voltage        | SIN, CLK, LATCH, RES, OSCI                         | 0                    | -   | 0.2 V <sub>DD</sub> | V    |

| VLED                | Pull-up Output Voltage for LED | SENSE                                              | -                    | -   | 6.3                 | V    |

| I <sub>OLED</sub>   | LED Driver Output Current      | LD1 to LD12                                        | 10                   | 30  | 50                  | mA   |

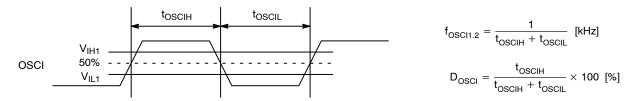

| f <sub>OSCI</sub> 1 | External Clock Operating       | OSCI (Figure 5)                                    | 190                  | 200 | 210                 | kHz  |

| f <sub>OSCI</sub> 2 | Frequency                      | OSCI (Figure 5)                                    | 142.5                | 150 | 157.5               |      |

| D <sub>OSCI</sub>   | External Clock Duty            | OSCI (Figure 5)                                    | 40                   | 50  | 60                  | %    |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

Figure 5. OSCI Pin Clock Timing

#### **ELECTRICAL CHARACTERISTICS** (for the recommended operating ranges)

| Symbol | Parameter                       | Pins                             | Conditions                                                             | Min                  | Тур                 | Max | Unit |

|--------|---------------------------------|----------------------------------|------------------------------------------------------------------------|----------------------|---------------------|-----|------|

| VH1    | Hysteresis                      | SIN, CLK,<br>LATCH, RES,<br>OSCI |                                                                        | -                    | 0.03V <sub>DD</sub> | -   | V    |

| IIH1   | Input High-level Current        | SIN, CLK,<br>LATCH, RES,<br>OSCI | VI = 5.5 V                                                             | -                    | -                   | 5.0 | μΑ   |

| IIH2   |                                 | SENSE                            | VI = 6.3 V, <del>RES</del> = "L"                                       | -                    | -                   | 5.0 | μΑ   |

| IIH3   |                                 | SENSE                            | VI = 6.3 V, <del>RES</del> = "H"                                       | -                    | -                   | 100 | μΑ   |

| IIL1   | Input Low-level Current         | SIN, CLK,<br>LATCH, RES,<br>OSCI | VI = 0 V                                                               | -5.0                 | -                   | -   | μΑ   |

| IIL2   |                                 | SENSE                            | VI = 0 V, <del>RES</del> = "L"                                         | -5.0                 | -                   | -   | μА   |

| IIL3   |                                 | SENSE                            | VI = 0 V, <del>RES</del> = "H"                                         | -5.0                 | -                   | -   | μА   |

| IOFFH1 | Output Off Leak Current         | ERR                              | VO = 5.5 V                                                             | -                    | -                   | 5.0 | μΑ   |

| IOFFH2 |                                 | LD1 to LD12                      | VO = 6.3 V                                                             | -                    | -                   | 5.0 |      |

| VOH1   | Output High-level<br>Voltage    | SOUT                             | IO = -4 mA                                                             | V <sub>DD</sub> -0.3 | -                   | -   | V    |

| VOL1   | Output Low-level Voltage        | SOUT, ERR                        | IO = 4 mA                                                              | -                    | -                   | 0.3 | V    |

| IACO1  | Output Current Accuracy         | LD1 to LD12                      | ID = 10 mA, V <sub>DD</sub> = 3.3 V, T <sub>A</sub> = 25°C             | <b>-</b> 5           | -                   | +5  | %    |

| IACO2  |                                 | LD1 to LD12                      | $ID = 30 \text{ mA}, V_{DD} = 3.3 \text{ V}, T_A = 25^{\circ}\text{C}$ | -5                   | -                   | +5  |      |

| IACO3  | ]                               | LD1 to LD12                      | ID = 50 mA, V <sub>DD</sub> = 3.3 V, T <sub>A</sub> = 25°C             | -5                   | -                   | +5  |      |

| VDET   | Power-down Detection<br>Voltage | VDD                              |                                                                        | 2.0                  | 2.2                 | 2.4 | V    |

#### **ELECTRICAL CHARACTERISTICS** (for the recommended operating ranges) (continued)

| Symbol            | Parameter                                        | Pins                  | Conditions                                                                                                                                                                           | Min  | Тур | Max  | Unit        |

|-------------------|--------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|-------------|

| VSES1             | LED Driver Supply                                | SENSE                 | V <sub>DD</sub> = 4.5 V to 5.5 V                                                                                                                                                     | 4.1  | 4.2 | 4.3  | V           |

| VSES2             | - Abnormally Voltage                             | SENSE                 | V <sub>DD</sub> = 2.7 V to 5.5 V                                                                                                                                                     | 2.3  | 2.4 | 2.5  |             |

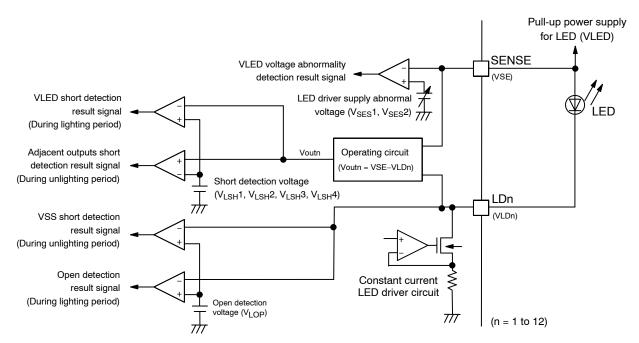

| VLOP              | Open Detection Voltage of the LED Driver Output  | LD1 to LD12           | Enabling the open or V <sub>SS</sub> short detection function of the LED driver output. (Figure 19, Figure 20)                                                                       | 0.4  | 0.5 | 0.6  | V           |

| VLSH1             | Short Detection Voltage of the LED Driver Output | LD1 to LD12           | Enabling the VLED short or adjacent outputs short detection function of the LED driver output. (When sets VSH = 0.8 V typ). V <sub>DD</sub> = 2.7 V to 5.5 V. (Figure 19, Figure 20) | 0.7  | 0.8 | 0.9  | V           |

| VLSH2             |                                                  | LD1 to LD12           | Enabling the VLED short or adjacent outputs short detection function of the LED driver output. (When sets VSH = 1.8 V typ). V <sub>DD</sub> = 2.7 V to 5.5 V. (Figure 19, Figure 20) | 1.65 | 1.8 | 1.95 | <b>&gt;</b> |

| VLSH3             |                                                  | LD1 to LD12           | Enabling the VLED short or adjacent outputs short detection function of the LED driver output. (When sets VSH = 2.8 V typ). V <sub>DD</sub> = 4.5 V to 5.5 V. (Figure 19, Figure 20) | 2.6  | 2.8 | 3.0  | \<br>\      |

| VLSH4             |                                                  | LD1 to LD12           | Enabling the VLED short or adjacent outputs short detection function of the LED driver output. (When sets VSH = 3.8 V typ). V <sub>DD</sub> = 4.5 V to 5.5 V. (Figure 19, Figure 20) | 3.55 | 3.8 | 4.05 | V           |

| fosc              | Oscillator Frequency                             | Oscillator<br>Circuit | Internal oscillator operating mode                                                                                                                                                   | 140  | 200 | 260  | kHz         |

| VREF              | Reference Voltage                                | IREF                  |                                                                                                                                                                                      | 1.1  | 1.2 | 1.23 | V           |

| TAC1              | Temperature Monitoring Accuracy                  |                       | Temperature accuracy sensing 125°C abnormality                                                                                                                                       | 125  | 135 | 150  | °C          |

| TAC2              |                                                  |                       | Temperature accuracy sensing 150°C abnormality                                                                                                                                       | 150  | 165 | -    | °C          |

| Thys              | Temperature Hysteresis                           |                       |                                                                                                                                                                                      | -    | 15  | _    | °C          |

| I <sub>DD</sub> 1 | Current Drain                                    | VDD                   | The reset of the system by the RES pin (RES = "L") V <sub>DD</sub> = 5.5 V                                                                                                           | -    | 1   | 15   | μA          |

| I <sub>DD</sub> 2 |                                                  | VDD                   | $V_{DD}$ = 5.5 V, Outputs are open. REXT = 12 k $\Omega$                                                                                                                             | -    | 2.5 | 5.0  | mA          |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

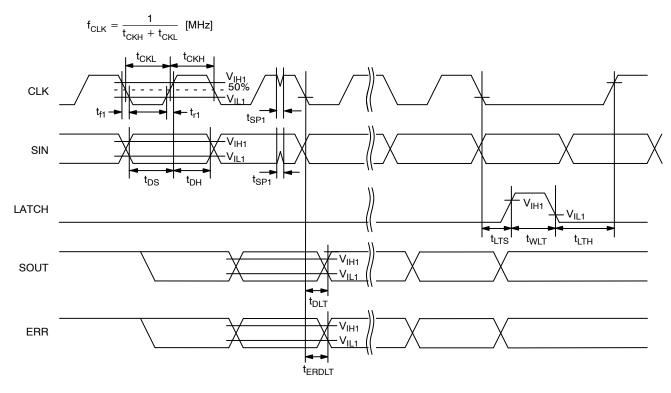

#### 4-LINE SERIAL BUS INTERFACE TIMING CHARACTERISTICS (for the recommended operating ranges)

| Symbol             | Parameter                    | Conditions                   | Min | Тур | Max  | Unit |

|--------------------|------------------------------|------------------------------|-----|-----|------|------|

| f <sub>CLK</sub>   | Clock Frequency              | CLK (Figure 6)               | -   | -   | 2    | MHz  |

| t <sub>CKH</sub>   | High-level Clock Pulse Width | CLK (Figure 6)               | 250 | -   | -    | ns   |

| t <sub>CKL</sub>   | Low-level Clock Pulse Width  | CLK (Figure 6)               | 250 | -   | -    | ns   |

| t <sub>DS</sub>    | Data Setup Time              | CLK, SIN (Figure 6)          | 100 | -   | -    | ns   |

| t <sub>DH</sub>    | Data Hold Time               | CLK, SIN (Figure 6)          | 100 | -   | -    | ns   |

| t <sub>r1</sub>    | Rise Time 1                  | CLK, SIN (Figure 6)          | -   | 100 | -    | ns   |

| t <sub>f1</sub>    | Fall Time 1                  | CLK, SIN (Figure 6)          | -   | 100 | -    | ns   |

| t <sub>LTS</sub>   | LATCH Setup Time             | CLK, LATCH (Figure 6)        | 200 | -   | -    | ns   |

| t <sub>LTH</sub>   | LATCH Hold Time              | CLK, LATCH (Figure 6)        | 200 | -   | -    | ns   |

| t <sub>WLT</sub>   | High-level LATCH Pulse Width | LATCH (Figure 6)             | 350 | -   | -    | ns   |

| t <sub>DLT</sub>   | SOUT Output Delay Time       | CLK, SOUT (Figure 6)         | -   | -   | 1500 | ns   |

| t <sub>ERDLT</sub> | ERR Output Delay Time        | CLK, ERR (Note 7) (Figure 6) | -   | -   | 1500 | ns   |

| t <sub>SP1</sub>   | Permission Noise Pulse Width | CLK, SIN, LATCH (Figure 6)   | -   | -   | 50   | ns   |

| t <sub>WRES</sub>  | Minimum Reset Pulse Width    | RES (Figures 19, 20, 24)     | 1   | _   | _    | ms   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

7. This item is the reference value when the pull-up register RPU = 4.7 kΩ and the load capacitance CL = 10 pF. The ERR pin is open drain output, so note that this value is changed according to RPU and CL.

Figure 6. Data Input and Data Output Timing of 4-line Serial Bus Interface

#### **FUNCTIONAL DESCRIPTION**

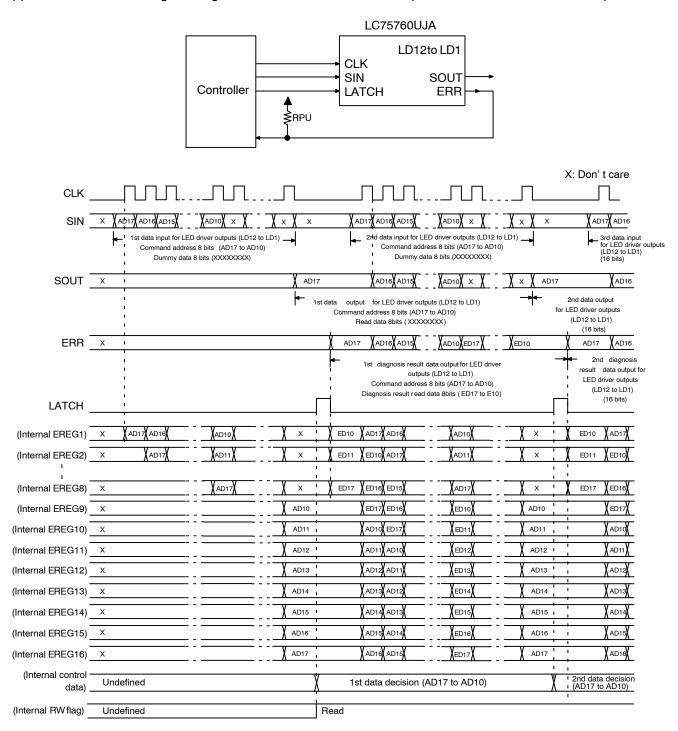

## Serial Data Transfer Format (In the Case of 4-line Serial Interface)

The 4-line serial interface is bidirectional serial interface using four bus lines of the CLK, SIN, SOUT and LATCH signal.

When a controller transmits data to this LSI, the controller transmits data (command address 8 bits, write data 8 bits) of 16 bits per one LSI to SIN pin in order of LSB from MSB and inputs LATCH signal. These serial data are received at the rising edge of the CLK signal. These data are latched and settled at the rising edge of the LATCH signal. When this LSI is a cascade connection, the controller inputs LATCH signal after having transmitted  $(16 \times n)$  bits to SIN pin.

When a controller receives data from this LSI, the controller transmits data (command address 8 bits, dummy

data 8 bits) of 16 bits per one LSI to SIN pin in order of LSB from MSB and inputs LATCH signal. These serial data are received at the rising edge of the CLK signal. This data is latched and settled at the rising edge of the LATCH signal. When read command address (ADn7 to ADn0) of higher 8 bits made a latch is distinguished from read command, read data (RDn7 to RDn0) is set to an internal shift register by a fall of the LATCH signal, and it is output to SOUT pin by a fall of the CLK signal. The controller can receive read data in a rising edge of the CLK signal. When this LSI does a cascade connection, the controller inputs LATCH signal after having transmitted  $(16 \times n)$  bits to SIN pin.

NOTE: n: The number of connection.

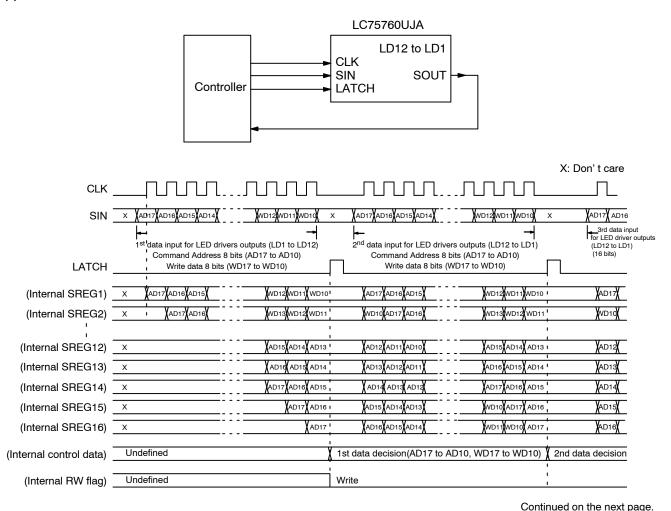

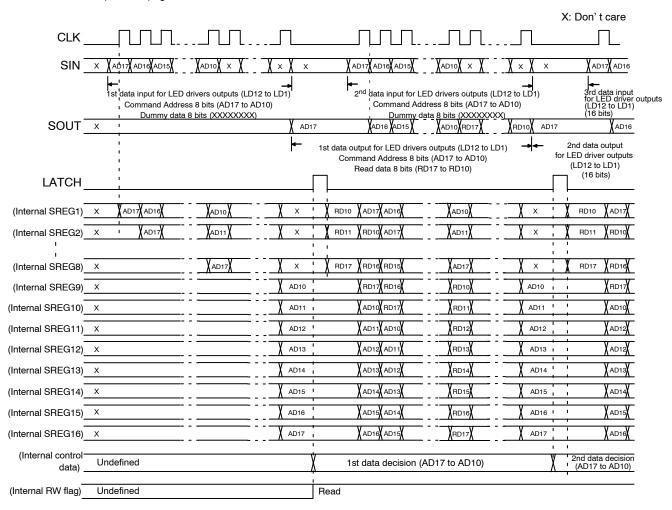

#### (1) In the Case of One Device Use

Figure 7. Transfer Example of Write Data of 4-line Serial Interface Using One Device

Continued from the previous page.

Figure 8. Transfer Example of Read Data of 4-line Serial Interface Using One Device

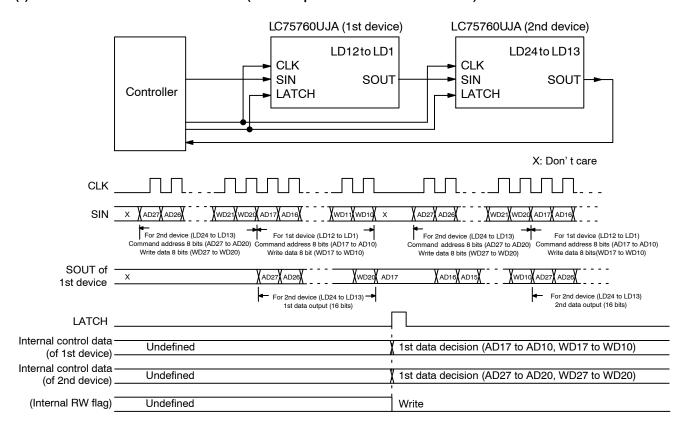

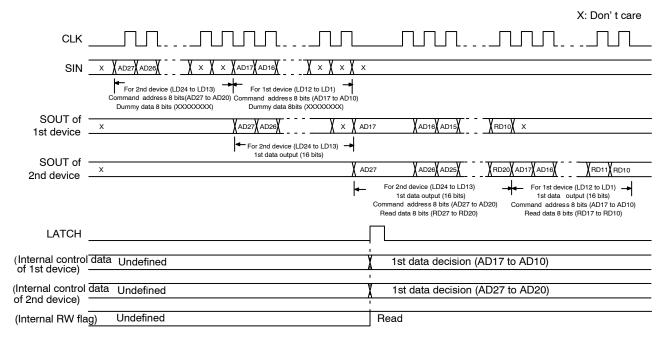

#### (2) In the Case of Cascade Connection (the Example of Two Device Connection)

Figure 9. Transfer Example of Write Data of 4-line Serial Interface using Cascade Connection (the Example of Two Device Connection)

Figure 10. Transfer Example of Read Data of 4-line Serial Interface using Cascade Connection (the Example of Two Device Connection)

#### (3) In the Case of Reading the Diagnosis Results Data from ERR Pin (When the Control Data ERD = "1")

Figure 11. Serial Data Transfer Example of Reading the Diagnosis Result Data from the ERR Pin

#### **List of Control Data**

Table 1. LIST OF WRITE COMMAND CONTROL REGISTERS

|                                        |    |      |      | C    | Command | Addres | s    |      |      |       |       |       | Write | Data  |       |       |       |

|----------------------------------------|----|------|------|------|---------|--------|------|------|------|-------|-------|-------|-------|-------|-------|-------|-------|

| Command Name                           | RW | ADn7 | ADn6 | ADn5 | ADn4    | ADn3   | ADn2 | ADn1 | ADn0 | WDn7  | WDn6  | WDn5  | WDn4  | WDn3  | WDn2  | WDn1  | WDn0  |

| Write output current regulation (LD1)  | W  | 0    | 0    | 0    | 0       | 0      | 0    | 0    | 1    | CA17  | CA16  | CA15  | CA14  | CA13  | CA12  | CA11  | CA10  |

| Write output current regulation (LD2)  | W  | 0    | 0    | 0    | 0       | 0      | 0    | 1    | 0    | CA27  | CA26  | CA25  | CA24  | CA23  | CA22  | CA21  | CA20  |

| Write output current regulation (LD3)  | W  | 0    | 0    | 0    | 0       | 0      | 0    | 1    | 1    | CA37  | CA36  | CA35  | CA34  | CA33  | CA32  | CA31  | CA30  |

| Write output current regulation (LD4)  | W  | 0    | 0    | 0    | 0       | 0      | 1    | 0    | 0    | CA47  | CA46  | CA45  | CA44  | CA43  | CA42  | CA41  | CA40  |

| Write output current regulation (LD5)  | W  | 0    | 0    | 0    | 0       | 0      | 1    | 0    | 1    | CA57  | CA56  | CA55  | CA54  | CA53  | CA52  | CA51  | CA50  |

| Write output current regulation (LD6)  | W  | 0    | 0    | 0    | 0       | 0      | 1    | 1    | 0    | CA67  | CA66  | CA65  | CA64  | CA63  | CA62  | CA61  | CA60  |

| Write output current regulation (LD7)  | W  | 0    | 0    | 0    | 0       | 0      | 1    | 1    | 1    | CA77  | CA76  | CA75  | CA74  | CA73  | CA72  | CA71  | CA70  |

| Write output current regulation (LD8)  | W  | 0    | 0    | 0    | 0       | 1      | 0    | 0    | 0    | CA87  | CA86  | CA85  | CA84  | CA83  | CA82  | CA81  | CA80  |

| Write output current regulation (LD9)  | W  | 0    | 0    | 0    | 0       | 1      | 0    | 0    | 1    | CA97  | CA96  | CA95  | CA94  | CA93  | CA92  | CA91  | CA90  |

| Write output current regulation (LD10) | W  | 0    | 0    | 0    | 0       | 1      | 0    | 1    | 0    | CA107 | CA106 | CA105 | CA104 | CA103 | CA102 | CA101 | CA100 |

| Write output current regulation (LD11) | W  | 0    | 0    | 0    | 0       | 1      | 0    | 1    | 1    | CA117 | CA116 | CA115 | CA114 | CA113 | CA112 | CA111 | CA110 |

| Write output current regulation (LD12) | W  | 0    | 0    | 0    | 0       | 1      | 1    | 0    | 0    | CA127 | CA126 | CA125 | CA124 | CA123 | CA122 | CA121 | CA120 |

| Write PWM Ch<br>(LD1,LD2)              | W  | 0    | 0    | 0    | 0       | 1      | 1    | 0    | 1    | х     | х     | L2C   | L2B   | L2A   | L1C   | L1B   | L1A   |

| Write PWM Ch<br>(LD3,LD4)              | W  | 0    | 0    | 0    | 0       | 1      | 1    | 1    | 0    | ×     | x     | L4C   | L4B   | L4A   | L3C   | L3B   | L3A   |

| Write PWM Ch<br>(LD5,LD6)              | W  | 0    | 0    | 0    | 0       | 1      | 1    | 1    | 1    | х     | х     | L6C   | L6B   | L6A   | L5C   | L5B   | L5A   |

| Write PWM Ch<br>(LD7,LD8)              | W  | 0    | 0    | 0    | 1       | 0      | 0    | 0    | 0    | х     | х     | L8C   | L8B   | L8A   | L7C   | L7B   | L7A   |

| Write PWM Ch<br>(LD9,LD10)             | W  | 0    | 0    | 0    | 1       | 0      | 0    | 0    | 1    | х     | х     | L10C  | L10B  | L10A  | L9C   | L9B   | L9A   |

| Write PWM Ch<br>(LD11,LD12)            | W  | 0    | 0    | 0    | 1       | 0      | 0    | 1    | 0    | х     | х     | L12C  | L12B  | L12A  | L11C  | L11B  | L11A  |

| Write PWM steps & PWM frame frequency  | W  | 0    | 0    | 0    | 1       | 0      | 0    | 1    | 1    | х     | х     | PF3   | PF2   | PF1   | PF0   | WN1   | WN0   |

| Write PWM data<br>(ch1-1)              | W  | 0    | 0    | 0    | 1       | 0      | 1    | 0    | 0    | х     | W19   | W18   | W17   | W16   | W15   | W14   | W13   |

| Write PWM data<br>(ch1-2)              | W  | 0    | 0    | 0    | 1       | 0      | 1    | 0    | 1    | х     | х     | х     | х     | х     | W12   | W11   | W10   |

| Write PWM data<br>(ch2-1)              | W  | 0    | 0    | 0    | 1       | 0      | 1    | 1    | 0    | ×     | W29   | W28   | W27   | W26   | W25   | W24   | W23   |

| Write PWM data<br>(ch2-2)              | W  | 0    | 0    | 0    | 1       | 0      | 1    | 1    | 1    | х     | х     | х     | х     | х     | W22   | W21   | W20   |

| Write PWM data<br>(ch3-1)              | W  | 0    | 0    | 0    | 1       | 1      | 0    | 0    | 0    | х     | W39   | W38   | W37   | W36   | W35   | W34   | W33   |

| Write PWM data<br>(ch3-2)              | W  | 0    | 0    | 0    | 1       | 1      | 0    | 0    | 1    | ×     | x     | x     | x     | x     | W32   | W31   | W30   |

| Write PWM data (ch4-1)                 | W  | 0    | 0    | 0    | 1       | 1      | 0    | 1    | 0    | х     | W49   | W48   | W47   | W46   | W45   | W44   | W43   |

| Write PWM data (ch4-2)                 | W  | 0    | 0    | 0    | 1       | 1      | 0    | 1    | 1    | х     | х     | х     | х     | х     | W42   | W41   | W40   |

| Write PWM data (ch5-1)                 | W  | 0    | 0    | 0    | 1       | 1      | 1    | 0    | 0    | х     | W59   | W58   | W57   | W56   | W55   | W54   | W53   |

| Write PWM data<br>(ch5-2)              | W  | 0    | 0    | 0    | 1       | 1      | 1    | 0    | 1    | х     | х     | х     | х     | х     | W52   | W51   | W50   |

| Write PWM data (ch6-1)                 | W  | 0    | 0    | 0    | 1       | 1      | 1    | 1    | 0    | х     | W69   | W68   | W67   | W66   | W65   | W64   | W63   |

| Write PWM data (ch6-2)                 | W  | 0    | 0    | 0    | 1       | 1      | 1    | 1    | 1    | х     | x     | x     | x     | х     | W62   | W61   | W60   |

| Write LED driver output mask 1         | W  | 0    | 0    | 1    | 0       | 0      | 0    | 0    | 0    | х     | х     | MLD6  | MLD5  | MLD4  | MLD3  | MLD2  | MLD1  |

Table 1. LIST OF WRITE COMMAND CONTROL REGISTERS (continued)

|                                                              |    |      | 1    |      | ommano | d Address | 5    | 1    | 1    |            |            |            | Write      | Data       |            | 1     |       |

|--------------------------------------------------------------|----|------|------|------|--------|-----------|------|------|------|------------|------------|------------|------------|------------|------------|-------|-------|

| Command Name                                                 | RW | ADn7 | ADn6 | ADn5 | ADn4   | ADn3      | ADn2 | ADn1 | ADn0 | WDn7       | WDn6       | WDn5       | WDn4       | WDn3       | WDn2       | WDn1  | WDn0  |

| Write LED driver output mask 2                               | W  | 0    | 0    | 1    | 0      | 0         | 0    | 0    | 1    | ×          | ×          | MLD12      | MLD11      | MLD10      | MLD9       | MLD8  | MLD7  |

| Write VLED short detection circuit mask 1                    | W  | 0    | 0    | 1    | 0      | 0         | 0    | 1    | 0    | ×          | х          | MSH6       | MSH5       | MSH4       | MSH3       | MSH2  | MSH1  |

| Write VLED short<br>detection circuit<br>mask 2              | W  | 0    | 0    | 1    | 0      | 0         | 0    | 1    | 1    | ×          | х          | MSH12      | MSH11      | MSH10      | MSH9       | MSH8  | MSH7  |

| Write VSS short<br>detection circuit<br>mask 1               | W  | 0    | 0    | 1    | 0      | 0         | 1    | 0    | 0    | ×          | х          | MSL6       | MSL5       | MSL4       | MSL3       | MSL2  | MSL1  |

| Write VSS short<br>detection circuit<br>mask 2               | W  | 0    | 0    | 1    | 0      | 0         | 1    | 0    | 1    | ×          | х          | MSL12      | MSL11      | MSL10      | MSL9       | MSL8  | MSL7  |

| Write open detection circuit mask 1                          | W  | 0    | 0    | 1    | 0      | 0         | 1    | 1    | 0    | х          | х          | MOP6       | MOP5       | MOP4       | MOP3       | MOP2  | MOP1  |

| Write open detection circuit mask 2                          | W  | 0    | 0    | 1    | 0      | 0         | 1    | 1    | 1    | х          | х          | MOP12      | MOP11      | MOP10      | MOP9       | MOP8  | MOP7  |

| Write VLED short<br>detection voltage<br>setting 1           | W  | 0    | 0    | 1    | 0      | 1         | 0    | 0    | 0    | VSH4B      | VSH4A      | VSH3B      | VSH3A      | VSH2B      | VSH2A      | VSH1B | VSH1A |

| Write VLED short<br>detection voltage<br>setting 2           | W  | 0    | 0    | 1    | 0      | 1         | 0    | 0    | 1    | VSH8B      | VSH8A      | VSH7B      | VSH7A      | VSH6B      | VSH6A      | VSH5B | VSH5A |

| Write VLED short<br>detection voltage<br>setting 3           | W  | 0    | 0    | 1    | 0      | 1         | 0    | 1    | 0    | VSH<br>12B | VSH<br>12A | VSH<br>11B | VSH<br>11A | VSH<br>10B | VSH<br>10A | VSH9B | VSH9A |

| Write control data 1                                         | W  | 0    | 0    | 1    | 0      | 1         | 0    | 1    | 1    | х          | х          | ERD        | SR         | EXF        | ОС         | TSDN  | PLDT  |

| Write control data 2                                         | W  | 0    | 0    | 1    | 0      | 1         | 1    | 0    | 0    | х          | MKAJ       | МКОР       | MKSL       | MKSH       | MKIR       | VLS1  | VLS0  |

| (Unused)                                                     | W  | 0    | 0    | 1    | 0      | 1         | 1    | 0    | 1    | х          | х          | х          | х          | х          | х          | х     | х     |

| :                                                            |    |      |      |      |        | :         |      |      |      |            |            |            | :          |            |            |       |       |

| (Unused)                                                     | W  | 0    | 0    | 1    | 1      | 0         | 0    | 0    | 0    | ×          | х          | х          | х          | х          | х          | х     | х     |

| Lock of output current regulation                            | W  | 0    | 0    | 1    | 1      | 0         | 0    | 0    | 1    | х          | х          | х          | х          | х          | х          | х     | х     |

| Lock of the PWM ch &<br>PWM steps & PWM<br>frame frequency   | W  | 0    | 0    | 1    | 1      | 0         | 0    | 1    | 0    | х          | х          | х          | х          | х          | х          | х     | х     |

| Lock of the PWM data                                         | W  | 0    | 0    | 1    | 1      | 0         | 0    | 1    | 1    | х          | х          | х          | х          | х          | х          | х     | х     |

| Lock of LED driver<br>output mask/open/<br>short             | W  | 0    | 0    | 1    | 1      | 0         | 1    | 0    | 0    | ×          | х          | х          | х          | х          | х          | х     | х     |

| Lock of control<br>data 1 & control data 2                   | W  | 0    | 0    | 1    | 1      | 0         | 1    | 0    | 1    | х          | х          | х          | х          | х          | х          | х     | х     |

| Unlock of output current regulation                          | W  | 0    | 0    | 1    | 1      | 0         | 1    | 1    | 0    | x          | х          | х          | х          | х          | х          | х     | х     |

| Unlock of the PWM ch<br>& PWM steps & PWM<br>frame frequency | W  | 0    | 0    | 1    | 1      | 0         | 1    | 1    | 1    | ×          | х          | х          | х          | ×          | х          | х     | х     |

| Unlock of the PWM data                                       | W  | 0    | 0    | 1    | 1      | 1         | 0    | 0    | 0    | ×          | х          | х          | х          | х          | х          | х     | х     |

| Unlock of LED driver output mask/open/ short                 | W  | 0    | 0    | 1    | 1      | 1         | 0    | 0    | 1    | ×          | х          | х          | х          | ×          | х          | х     | x     |

| Unlock of control data 1 & control data 2                    | W  | 0    | 0    | 1    | 1      | 1         | 0    | 1    | 0    | х          | х          | х          | х          | х          | х          | х     | х     |

| Reset POR flag                                               | W  | 0    | 0    | 1    | 1      | 1         | 0    | 1    | 1    | х          | ×          | ×          | ×          | х          | ×          | х     | х     |

| Reset Status flag                                            | W  | 0    | 0    | 1    | 1      | 1         | 1    | 0    | 0    | х          | х          | х          | х          | х          | х          | х     | х     |

| Software reset                                               | W  | 0    | 0    | 1    | 1      | 1         | 1    | 0    | 1    | х          | x          | x          | x          | х          | x          | х     | х     |

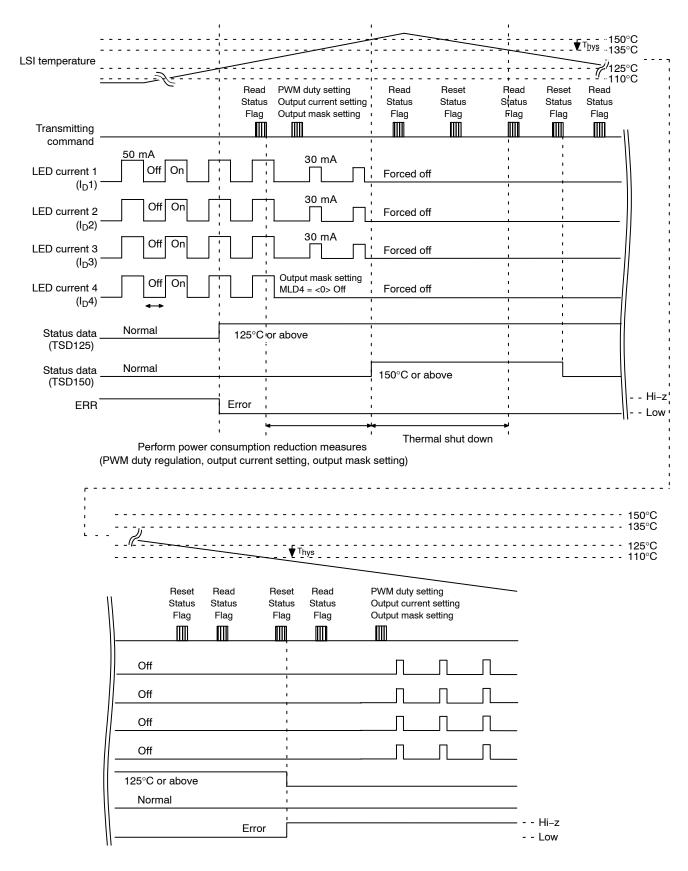

| Clearing of the fundamental clock abnormality                | W  | 0    | 0    | 1    | 1      | 1         | 1    | 1    | 0    | ×          | х          | х          | х          | х          | х          | х     | х     |

| Check of the fundamental clock abnormality                   | W  | 0    | 0    | 1    | 1      | 1         | 1    | 1    | 1    | х          | х          | х          | х          | х          | х          | х     | х     |

| (Unused)                                                     | W  | 0    | 1    | 0    | 0      | 0         | 0    | 0    | 0    | х          | х          | х          | х          | х          | х          | х     | х     |

| :                                                            |    |      |      |      | :      | :         |      |      |      |            |            |            | :          |            |            |       |       |

| (Unused)                                                     | W  | 0    | 1    | 1    | 1      | 1         | 1    | 1    | 1    | ×          | ×          | ×          | х          | ×          | ×          | x     | х     |

<sup>8.</sup> n: The number of the connection, x: Don't care.

Table 2. LIST OF READ COMMAND CONTROL REGISTERS

|                                       |    |      |      | C    | Command | Addres | s    |      |      |       |       |       | Read  | Data  |       |       |       |

|---------------------------------------|----|------|------|------|---------|--------|------|------|------|-------|-------|-------|-------|-------|-------|-------|-------|

| Command Name                          | RW | ADn7 | ADn6 | ADn5 | ADn4    | ADn3   | ADn2 | ADn1 | ADn0 | RDn7  | RDn6  | RDn5  | RDn4  | RDn3  | RDn2  | RDn1  | RDn0  |

| Read output current regulation (LD1)  | R  | 1    | 0    | 0    | 0       | 0      | 0    | 0    | 1    | CA17  | CA16  | CA15  | CA14  | CA13  | CA12  | CA11  | CA10  |

| Read output current regulation (LD2)  | R  | 1    | 0    | 0    | 0       | 0      | 0    | 1    | 0    | CA27  | CA26  | CA25  | CA24  | CA23  | CA22  | CA21  | CA20  |

| Read output current regulation (LD3)  | R  | 1    | 0    | 0    | 0       | 0      | 0    | 1    | 1    | CA37  | CA36  | CA35  | CA34  | CA33  | CA32  | CA31  | CA30  |

| Read output current regulation (LD4)  | R  | 1    | 0    | 0    | 0       | 0      | 1    | 0    | 0    | CA47  | CA46  | CA45  | CA44  | CA43  | CA42  | CA41  | CA40  |

| Read output current regulation (LD5)  | R  | 1    | 0    | 0    | 0       | 0      | 1    | 0    | 1    | CA57  | CA56  | CA55  | CA54  | CA53  | CA52  | CA51  | CA50  |

| Read output current regulation (LD6)  | R  | 1    | 0    | 0    | 0       | 0      | 1    | 1    | 0    | CA67  | CA66  | CA65  | CA64  | CA63  | CA62  | CA61  | CA60  |

| Read output current regulation (LD7)  | R  | 1    | 0    | 0    | 0       | 0      | 1    | 1    | 1    | CA77  | CA76  | CA75  | CA74  | CA73  | CA72  | CA71  | CA70  |

| Read output current regulation (LD8)  | R  | 1    | 0    | 0    | 0       | 1      | 0    | 0    | 0    | CA87  | CA86  | CA85  | CA84  | CA83  | CA82  | CA81  | CA80  |

| Read output current regulation (LD9)  | R  | 1    | 0    | 0    | 0       | 1      | 0    | 0    | 1    | CA97  | CA96  | CA95  | CA94  | CA93  | CA92  | CA91  | CA90  |

| Read output current regulation (LD10) | R  | 1    | 0    | 0    | 0       | 1      | 0    | 1    | 0    | CA107 | CA106 | CA105 | CA104 | CA103 | CA102 | CA101 | CA100 |

| Read output current regulation (LD11) | R  | 1    | 0    | 0    | 0       | 1      | 0    | 1    | 1    | CA117 | CA116 | CA115 | CA114 | CA113 | CA112 | CA111 | CA110 |

| Read output current regulation (LD12) | R  | 1    | 0    | 0    | 0       | 1      | 1    | 0    | 0    | CA127 | CA126 | CA125 | CA124 | CA123 | CA122 | CA121 | CA120 |

| Read PWM ch<br>(LD1,LD2)              | R  | 1    | 0    | 0    | 0       | 1      | 1    | 0    | 1    | 0     | 0     | L2C   | L2B   | L2A   | L1C   | L1B   | L1A   |

| Read PWM ch<br>(LD3,LD4)              | R  | 1    | 0    | 0    | 0       | 1      | 1    | 1    | 0    | 0     | 0     | L4C   | L4B   | L4A   | L3C   | L3B   | L3A   |

| Read PWM ch<br>(LD5,LD6)              | R  | 1    | 0    | 0    | 0       | 1      | 1    | 1    | 1    | 0     | 0     | L6C   | L6B   | L6A   | L5C   | L5B   | L5A   |

| Read PWM ch<br>(LD7,LD8)              | R  | 1    | 0    | 0    | 1       | 0      | 0    | 0    | 0    | 0     | 0     | L8C   | L8B   | L8A   | L7C   | L7B   | L7A   |

| Read PWM ch<br>(LD9,LD10)             | R  | 1    | 0    | 0    | 1       | 0      | 0    | 0    | 1    | 0     | 0     | L10C  | L10B  | L10A  | L9C   | L9B   | L9A   |

| Read PWM ch<br>(LD11,LD12)            | R  | 1    | 0    | 0    | 1       | 0      | 0    | 1    | 0    | 0     | 0     | L12C  | L12B  | L12A  | L11C  | L11B  | L11A  |

| Read PWM steps & PWM frame frequency  | R  | 1    | 0    | 0    | 1       | 0      | 0    | 1    | 1    | 0     | 0     | PF3   | PF2   | PF1   | PF0   | WN1   | WN0   |

| Read PWM data<br>(ch1-1)              | R  | 1    | 0    | 0    | 1       | 0      | 1    | 0    | 0    | 0     | W19   | W18   | W17   | W16   | W15   | W14   | W13   |

| Read PWM data<br>(ch1-2)              | R  | 1    | 0    | 0    | 1       | 0      | 1    | 0    | 1    | 0     | 0     | 0     | 0     | 0     | W12   | W11   | W10   |

| Read PWM data<br>(ch2-1)              | R  | 1    | 0    | 0    | 1       | 0      | 1    | 1    | 0    | 0     | W29   | W28   | W27   | W26   | W25   | W24   | W23   |

| Read PWM data<br>(ch2-2)              | R  | 1    | 0    | 0    | 1       | 0      | 1    | 1    | 1    | 0     | 0     | 0     | 0     | 0     | W22   | W21   | W20   |

| Read PWM data<br>(ch3-1)              | R  | 1    | 0    | 0    | 1       | 1      | 0    | 0    | 0    | 0     | W39   | W38   | W37   | W36   | W35   | W34   | W33   |

| Read PWM data<br>(ch3-2)              | R  | 1    | 0    | 0    | 1       | 1      | 0    | 0    | 1    | 0     | 0     | 0     | 0     | 0     | W32   | W31   | W30   |

| Read PWM data<br>(ch4-1)              | R  | 1    | 0    | 0    | 1       | 1      | 0    | 1    | 0    | 0     | W49   | W48   | W47   | W46   | W45   | W44   | W43   |

| Read PWM data<br>(ch4-2)              | R  | 1    | 0    | 0    | 1       | 1      | 0    | 1    | 1    | 0     | 0     | 0     | 0     | 0     | W42   | W41   | W40   |

| Read PWM data<br>(ch5-1)              | R  | 1    | 0    | 0    | 1       | 1      | 1    | 0    | 0    | 0     | W59   | W58   | W57   | W56   | W55   | W54   | W53   |

| Read PWM data<br>(ch5-2)              | R  | 1    | 0    | 0    | 1       | 1      | 1    | 0    | 1    | 0     | 0     | 0     | 0     | 0     | W52   | W51   | W50   |

| Read PWM data<br>(ch6-1)              | R  | 1    | 0    | 0    | 1       | 1      | 1    | 1    | 0    | 0     | W69   | W68   | W67   | W66   | W65   | W64   | W63   |

| Read PWM data<br>(ch6-2)              | R  | 1    | 0    | 0    | 1       | 1      | 1    | 1    | 1    | 0     | 0     | 0     | 0     | 0     | W62   | W61   | W60   |

| Read LED driver output mask 1         | R  | 1    | 0    | 1    | 0       | 0      | 0    | 0    | 0    | 0     | 0     | MLD6  | MLD5  | MLD4  | MLD3  | MLD2  | MLD1  |

| Read LED driver output mask 2         | R  | 1    | 0    | 1    | 0       | 0      | 0    | 0    | 1    | 0     | 0     | MLD12 | MLD11 | MLD10 | MLD9  | MLD8  | MLD7  |

Table 2. LIST OF READ COMMAND CONTROL REGISTERS (continued)

|                                                   |    | Command Address |      |      |      |      |      |      | Read Data |            |            |            |            |            |            |           |           |

|---------------------------------------------------|----|-----------------|------|------|------|------|------|------|-----------|------------|------------|------------|------------|------------|------------|-----------|-----------|

| Command Name                                      | RW | ADn7            | ADn6 | ADn5 | ADn4 | ADn3 | ADn2 | ADn1 | ADn0      | RDn7       | RDn6       | RDn5       | RDn4       | RDn3       | RDn2       | RDn1      | RDn0      |

| Read VLED short<br>detection circuit<br>mask 1    | R  | 1               | 0    | 1    | 0    | 0    | 0    | 1    | 0         | 0          | 0          | MSH6       | MSH5       | MSH4       | MSH3       | MSH2      | MSH1      |

| Read VLED short<br>detection circuit<br>mask 2    | R  | 1               | 0    | 1    | 0    | 0    | 0    | 1    | 1         | 0          | 0          | MSH12      | MSH11      | MSH10      | MSH9       | MSH8      | MSH7      |

| Read VSS short<br>detection circuit<br>mask 1     | R  | 1               | 0    | 1    | 0    | 0    | 1    | 0    | 0         | 0          | 0          | MSL6       | MSL5       | MSL4       | MSL3       | MSL2      | MSL1      |

| Read VSS short<br>detection circuit<br>mask 2     | R  | 1               | 0    | 1    | 0    | 0    | 1    | 0    | 1         | 0          | 0          | MSL12      | MSL11      | MSL10      | MSL9       | MSL8      | MSL7      |

| Read open detection circuit mask 1                | R  | 1               | 0    | 1    | 0    | 0    | 1    | 1    | 0         | 0          | 0          | MOP6       | MOP5       | MOP4       | МОР3       | MOP2      | MOP1      |

| Read open detection circuit mask 2                | R  | 1               | 0    | 1    | 0    | 0    | 1    | 1    | 1         | 0          | 0          | MOP12      | MOP11      | MOP10      | MOP9       | MOP8      | MOP7      |

| Read VLED short<br>detection voltage<br>setting 1 | R  | 1               | 0    | 1    | 0    | 1    | 0    | 0    | 0         | VSH4B      | VSH4A      | VSH3B      | VSH3A      | VSH2B      | VSH2A      | VSH1B     | VSH1A     |

| Read VLED short<br>detection voltage<br>setting 2 | R  | 1               | 0    | 1    | 0    | 1    | 0    | 0    | 1         | VSH8B      | VSH8A      | VSH7B      | VSH7A      | VSH6B      | VSH6A      | VSH5B     | VSH5A     |

| Read VLED short<br>detection voltage<br>setting 3 | R  | 1               | 0    | 1    | 0    | 1    | 0    | 1    | 0         | VSH<br>12B | VSH<br>12A | VSH<br>11B | VSH<br>11A | VSH<br>10B | VSH<br>10A | VSH9B     | VSH9A     |

| Read control data 1                               | R  | 1               | 0    | 1    | 0    | 1    | 0    | 1    | 1         | 0          | 0          | ERD        | SR         | EXF        | ОС         | TSDN      | PLDT      |

| Read control data 2                               | R  | 1               | 0    | 1    | 0    | 1    | 1    | 0    | 0         | 0          | MKAJ       | МКОР       | MKSL       | MKSH       | MKIR       | VLS1      | VLS0      |

| (Unused)                                          | R  | 1               | 0    | 1    | 0    | 1    | 1    | 0    | 1         | х          | х          | х          | х          | х          | х          | х         | х         |

| :                                                 |    |                 |      |      | :    |      | •    | •    | •         |            | •          | •          | :          | :          | •          | •         | •         |

| (Unused)                                          | R  | 1               | 1    | 0    | 0    | 0    | 0    | 0    | 0         | ×          | х          | х          | х          | х          | х          | х         | х         |

| Read Status flag 1                                | R  | 1               | 1    | 0    | 0    | 0    | 0    | 0    | 1         | POR        | CERR       | VERR       | AERR       | OERR       | SERR       | TSD150    | TSD125    |

| Read Status flag 2                                | R  | 1               | 1    | 0    | 0    | 0    | 0    | 1    | 0         | 0          | 0          | 0          | R<br>LOČK  | W<br>LOCK  | P<br>LOČK  | M<br>LOCK | C<br>LOCK |

| Read External resistance diagnosis result         | R  | 1               | 1    | 0    | 0    | 0    | 0    | 1    | 1         | 0          | 0          | 0          | 0          | 0          | 0          | IR1       | IR0       |

| Read VLED short detection result 1                | R  | 1               | 1    | 0    | 0    | 0    | 1    | 0    | 0         | 0          | 0          | RSH6       | RSH5       | RSH4       | RSH3       | RSH2      | RSH1      |

| Read VLED short detection result 2                | R  | 1               | 1    | 0    | 0    | 0    | 1    | 0    | 1         | 0          | 0          | RSH12      | RSH11      | RSH10      | RSH9       | RSH8      | RSH7      |

| Read VSS short detection result 1                 | R  | 1               | 1    | 0    | 0    | 0    | 1    | 1    | 0         | 0          | 0          | RSL6       | RSL5       | RSL4       | RSL3       | RSL2      | RSL1      |

| Read VSS short<br>detection result 2              | R  | 1               | 1    | 0    | 0    | 0    | 1    | 1    | 1         | 0          | 0          | RSL12      | RSL11      | RSL10      | RSL9       | RSL8      | RSL7      |

| Read open detection result 1                      | R  | 1               | 1    | 0    | 0    | 1    | 0    | 0    | 0         | 0          | 0          | ROP6       | ROP5       | ROP4       | ROP3       | ROP2      | ROP1      |

| Read open detection result 2                      | R  | 1               | 1    | 0    | 0    | 1    | 0    | 0    | 1         | 0          | 0          | ROP12      | ROP11      | ROP10      | ROP9       | ROP8      | ROP7      |

| Read adjacent outputs short detection result 1    | R  | 1               | 1    | 0    | 0    | 1    | 0    | 1    | 0         | 0          | 0          | RAJ6       | RAJ5       | RAJ4       | RAJ3       | RAJ2      | RAJ1      |

| Read adjacent outputs short detection result 2    | R  | 1               | 1    | 0    | 0    | 1    | 0    | 1    | 1         | 0          | 0          | RAJ12      | RAJ11      | RAJ10      | RAJ9       | RAJ8      | RAJ7      |

| Read the state data of the LED driver output 1    | R  | 1               | 1    | 0    | 0    | 1    | 1    | 0    | 0         | 0          | 0          | RLD6       | RLD5       | RLD4       | RLD3       | RLD2      | RLD1      |

| Read the state data of the LED driver output 2    | R  | 1               | 1    | 0    | 0    | 1    | 1    | 0    | 1         | 0          | 0          | RLD12      | RLD11      | RLD10      | RLD9       | RLD8      | RLD7      |

| (Unused)                                          | R  | 1               | 1    | 0    | 0    | 1    | 1    | 1    | 0         | х          | х          | х          | х          | х          | х          | х         | х         |

| (Unused)                                          | R  | 1               | 1    | 0    | 0    | 1    | 1    | 1    | 1         | х          | х          | х          | х          | х          | х          | х         | х         |

| :                                                 |    |                 |      | ı    | :    |      | 1    | 1    | 1         |            | 1          | 1          | :          | 1          | 1          | 1         | 1         |

| (Unused)                                          | R  | 1               | 1    | 1    | 1    | 1    | 1    | 1    | 1         | х          | x          | ×          | x          | x          | x          | x         | x         |

<sup>9.</sup> n: The number of the connection, x: Don't care.

#### **Control Data Functions**

(1) CA17 to CA10, CA27 to CA20, CA37 to CA30, CA47 to CA40, CA57 to CA50, CA67 to CA60, CA77 to CA70, CA87 to CA80, CA97 to CA90, CA107 to CA100, CA117 to CA110, CA127 to CA120 • • • Control Data for Current Value (ID) Setting of the LED Driver Output

By these control data, the current value(ID) of the LED driver output (LD1 to LD12) is set in each ch. Reference current (IREF) is decided by an external resistor connected to IREF pin, and peak output current (IDmax) of the LED driver output is IREF x 500. In addition, these control data

| CA- |                                      |

|-----|-----|-----|-----|-----|-----|-----|-----|--------------------------------------|

| n7  | n6  | n5  | n4  | n3  | n2  | n1  | n0  | Output Current Value (ID)            |

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | (1/256) x (I <sub>REF</sub> x 500)   |

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | (2/256) x (I <sub>REF</sub> x 500)   |

| 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   | (3/256) x (I <sub>REF</sub> x 500)   |

| 0   | 0   | 0   | 0   | 0   | 0   | 1   | 1   | (4/256) x (I <sub>REF</sub> x 500)   |

| 0   | 0   | 0   | 0   | 0   | 1   | 0   | 0   | (5/256) x (I <sub>REF</sub> x 500)   |

| 0   | 0   | 0   | 0   | 0   | 1   | 0   | 1   | (6/256) x (I <sub>REF</sub> x 500)   |

| 0   | 0   | 0   | 0   | 0   | 1   | 1   | 0   | (7/256) x (I <sub>REF</sub> x 500)   |

| 0   | 0   | 0   | 0   | 0   | 1   | 1   | 1   | (8/256) x (I <sub>REF</sub> x 500)   |

| 0   | 0   | 0   | 0   | 1   | 0   | 0   | 0   | (9/256) x (I <sub>REF</sub> x 500)   |

| 0   | 0   | 0   | 0   | 1   | 0   | 0   | 1   | (10/256) x (I <sub>REF</sub> x 500)  |

| 0   | 0   | 0   | 0   | 1   | 0   | 1   | 0   | (11/256) x (I <sub>REF</sub> x 500)  |

| 0   | 0   | 0   | 0   | 1   | 0   | 1   | 1   | (12/256) x (I <sub>REF</sub> x 500)  |

| 0   | 0   | 0   | 0   | 1   | 1   | 0   | 0   | (13/256) x (I <sub>REF</sub> x 500)  |

| 0   | 0   | 0   | 0   | 1   | 1   | 0   | 1   | (14/256) x (I <sub>REF</sub> x 500)  |

| 0   | 0   | 0   | 0   | 1   | 1   | 1   | 0   | (15/256) x (I <sub>REF</sub> x 500)  |

| 0   | 0   | 0   | 0   | 1   | 1   | 1   | 1   | (16/256) x (I <sub>REF</sub> x 500)  |

| :   | :   | :   | :   | :   | :   | :   | :   | :                                    |

| 0   | 1   | 1   | 1   | 0   | 0   | 0   | 0   | (113/256) x (I <sub>REF</sub> x 500) |

| 0   | 1   | 1   | 1   | 0   | 0   | 0   | 1   | (114/256) x (I <sub>REF</sub> x 500) |

| 0   | 1   | 1   | 1   | 0   | 0   | 1   | 0   | (115/256) x (I <sub>REF</sub> x 500) |

| 0   | 1   | 1   | 1   | 0   | 0   | 1   | 1   | (116/256) x (I <sub>REF</sub> x 500) |

| 0   | 1   | 1   | 1   | 0   | 1   | 0   | 0   | (117/256) x (I <sub>REF</sub> x 500) |

| 0   | 1   | 1   | 1   | 0   | 1   | 0   | 1   | (118/256) x (I <sub>REF</sub> x 500) |

| 0   | 1   | 1   | 1   | 0   | 1   | 1   | 0   | (119/256) x (I <sub>REF</sub> x 500) |

| 0   | 1   | 1   | 1   | 0   | 1   | 1   | 1   | (120/256) x (I <sub>REF</sub> x 500) |

| 0   | 1   | 1   | 1   | 1   | 0   | 0   | 0   | (121/256) x (I <sub>REF</sub> x 500) |

| 0   | 1   | 1   | 1   | 1   | 0   | 0   | 1   | (122/256) x (I <sub>REF</sub> x 500) |

| 0   | 1   | 1   | 1   | 1   | 0   | 1   | 0   | (123/256) x (I <sub>REF</sub> x 500) |

| 0   | 1   | 1   | 1   | 1   | 0   | 1   | 1   | (124/256) x (I <sub>REF</sub> x 500) |

| 0   | 1   | 1   | 1   | 1   | 1   | 0   | 0   | (125/256) x (I <sub>REF</sub> x 500) |

| 0   | 1   | 1   | 1   | 1   | 1   | 0   | 1   | (126/256) x (I <sub>REF</sub> x 500) |

| 0   | 1   | 1   | 1   | 1   | 1   | 1   | 0   | (127/256) x (I <sub>REF</sub> x 500) |

| 0   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | (128/256) x (I <sub>REF</sub> x 500) |

| CA-<br>n7 | CA-<br>n6 | CA-<br>n5 | CA-<br>n4 | CA-<br>n3 | CA-<br>n2 | CA-<br>n1 | CA-<br>n0 | Output Current Value (ID)            |  |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|--------------------------------------|--|

| 1         | 0         | 0         | 0         | 0         | 0         | 0         | 0         | (129/256) x (I <sub>REF</sub> x 500) |  |

| 1         | 0         | 0         | 0         | 0         | 0         | 0         | 1         | (130/256) x (I <sub>REF</sub> x 500) |  |

| 1         | 0         | 0         | 0         | 0         | 0         | 1         | 0         | (131/256) x (I <sub>REF</sub> x 500) |  |

| 1         | 0         | 0         | 0         | 0         | 0         | 1         | 1         | (132/256) x (I <sub>REF</sub> x 500) |  |

| 1         | 0         | 0         | 0         | 0         | 1         | 0         | 0         | (133/256) x (I <sub>REF</sub> x 500) |  |

| 1         | 0         | 0         | 0         | 0         | 1         | 0         | 1         | (134/256) x (I <sub>REF</sub> x 500) |  |

| 1         | 0         | 0         | 0         | 0         | 1         | 1         | 0         | (135/256) x (I <sub>REF</sub> x 500) |  |

| 1         | 0         | 0         | 0         | 0         | 1         | 1         | 1         | (136/256) x (I <sub>REF</sub> x 500) |  |

| 1         | 0         | 0         | 0         | 1         | 0         | 0         | 0         | (137/256) x (I <sub>REF</sub> x 500) |  |

| 1         | 0         | 0         | 0         | 1         | 0         | 0         | 1         | (138/256) x (I <sub>REF</sub> x 500) |  |

| 1         | 0         | 0         | 0         | 1         | 0         | 1         | 0         | (139/256) x (I <sub>REF</sub> x 500) |  |

| 1         | 0         | 0         | 0         | 1         | 0         | 1         | 1         | (140/256) x (I <sub>REF</sub> x 500) |  |

| 1         | 0         | 0         | 0         | 1         | 1         | 0         | 0         | (141/256) x (I <sub>REF</sub> x 500) |  |

| 1         | 0         | 0         | 0         | 1         | 1         | 0         | 1         | (142/256) x (I <sub>REF</sub> x 500) |  |

| 1         | 0         | 0         | 0         | 1         | 1         | 1         | 0         | (143/256) x (I <sub>REF</sub> x 500) |  |

| 1         | 0         | 0         | 0         | 1         | 1         | 1         | 1         | (144/256) x (I <sub>REF</sub> x 500) |  |

| :         | :         | :         | :         | :         | :         | :         | :         | :                                    |  |

| 1         | 1         | 1         | 1         | 0         | 0         | 0         | 0         | (241/256) x (I <sub>REF</sub> x 500) |  |

| 1         | 1         | 1         | 1         | 0         | 0         | 0         | 1         | (242/256) x (I <sub>REF</sub> x 500) |  |

| 1         | 1         | 1         | 1         | 0         | 0         | 1         | 0         | (243/256) x (I <sub>REF</sub> x 500) |  |

| 1         | 1         | 1         | 1         | 0         | 0         | 1         | 1         | (244/256) x (I <sub>REF</sub> x 500) |  |

| 1         | 1         | 1         | 1         | 0         | 1         | 0         | 0         | (245/256) x (I <sub>REF</sub> x 500) |  |

| 1         | 1         | 1         | 1         | 0         | 1         | 0         | 1         | (246/256) x (I <sub>REF</sub> x 500) |  |

| 1         | 1         | 1         | 1         | 0         | 1         | 1         | 0         | (247/256) x (I <sub>REF</sub> x 500) |  |

| 1         | 1         | 1         | 1         | 0         | 1         | 1         | 1         | (248/256) x (I <sub>REF</sub> x 500) |  |

| 1         | 1         | 1         | 1         | 1         | 0         | 0         | 0         | (249/256) x (I <sub>REF</sub> x 500) |  |

| 1         | 1         | 1         | 1         | 1         | 0         | 0         | 1         | (250/256) x (I <sub>REF</sub> x 500) |  |

| 1         | 1         | 1         | 1         | 1         | 0         | 1         | 0         | (251/256) x (I <sub>REF</sub> x 500) |  |

| 1         | 1         | 1         | 1         | 1         | 0         | 1         | 1         | (252/256) x (I <sub>REF</sub> x 500) |  |

| 1         | 1         | 1         | 1         | 1         | 1         | 0         | 0         | (253/256) x (I <sub>REF</sub> x 500) |  |

| 1         | 1         | 1         | 1         | 1         | 1         | 0         | 1         | (254/256) x (I <sub>REF</sub> x 500) |  |

| 1         | 1         | 1         | 1         | 1         | 1         | 1         | 0         | (255/256) x (I <sub>REF</sub> x 500) |  |

| 1         | 1         | 1         | 1         | 1         | 1         | 1         | 1         | (256/256) x (I <sub>REF</sub> x 500) |  |

```

10. CA17 to CA10: Data for current value setting of the LED driver output (LD1) / CA27 to CA20: Data for current value setting of the LED driver output (LD2) / CA37 to CA30: Data for current value setting of the LED driver output (LD3) / CA47 to CA40: Data for current value setting of the LED driver output (LD4) / CA57 to CA50: Data for current value setting of the LED driver output (LD5) / CA67 to CA60: Data for current value setting of the LED driver output (LD6) / CA77 to CA70: Data for current value setting of the LED driver output (LD7) / CA87 to CA80: Data for current value setting of the LED driver output (LD8) / CA97 to CA90: Data for current value setting of the LED driver output (LD9) / CA107 to CA100: Data for current value setting of the LED driver output (LD10) / CA117 to CA110: Data for current value setting of the LED driver output (LD11) / CA127 to CA120: Data for current value setting of the LED driver output (LD11)

```

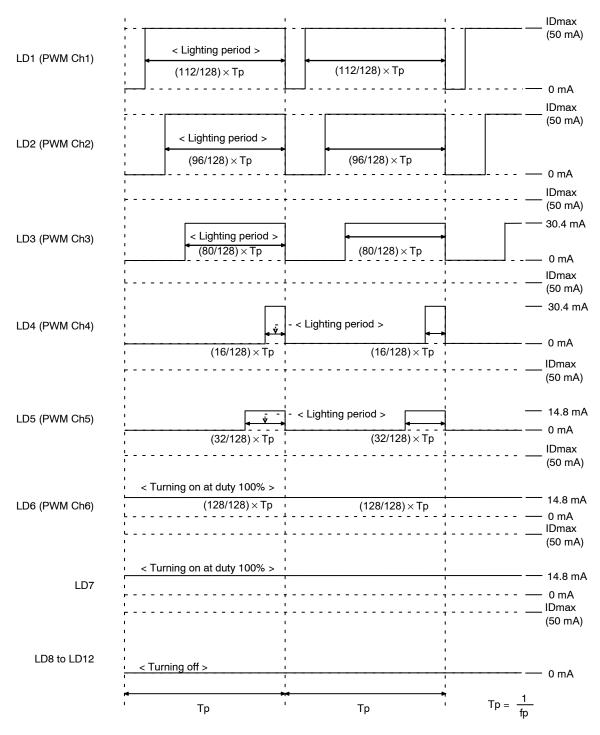

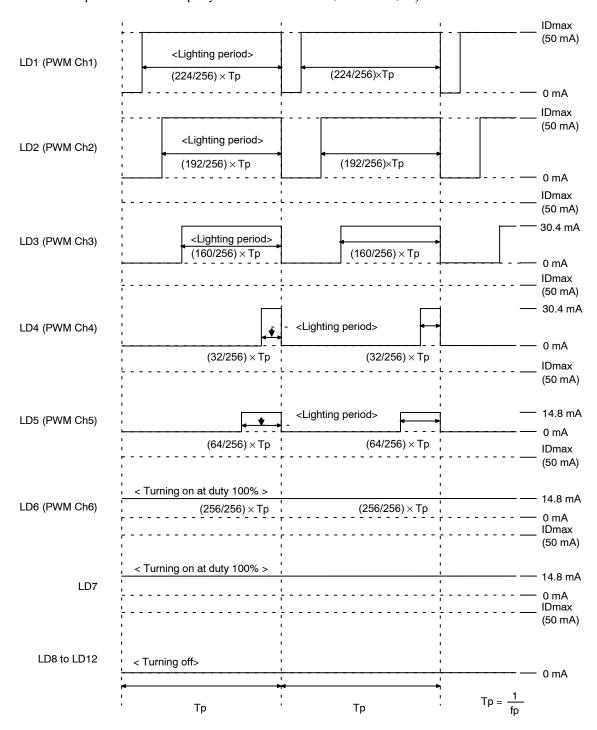

# (2) L1C, L1B, L1A to L12C, L12B, L12A • • • Control Data for Ch Setting of the PWM Circuits that Adjust Brightness of LED

By these control data, the PWM circuit of the LED driver output is set in each Ch. In addition, these control data are protected by the command [Lock of the PWM ch & PWM steps & PWM frame frequency]. It cannot change these control data when the command [Lock of the PWM ch &

PWM steps & PWM frame frequency] is set. When changing these control data, transmit the command [Unlock of the PWM ch & PWM steps & PWM frame frequency]. Afterwards set these control data. These control data are initialized to "(LnC, LnB, LnA) = (0, 0, 1)" all by the reset action (reset by  $\overline{RES}$  pin, voltage detection type reset circuit (VDET), software reset or the thermal shut down actuating) of the system.

| LnC | LnB | LnA | Ch of the PWM Circuit for LED Driver Output LDn                                            |

|-----|-----|-----|--------------------------------------------------------------------------------------------|

| 0   | 0   | 0   | PWM circuit is not selected. (The setting of turning on/off of the duty 100% is possible.) |

| 0   | 0   | 1   | PWM circuit (Ch1) is selected.                                                             |

| 0   | 1   | 0   | PWM circuit (Ch2) is selected.                                                             |

| 0   | 1   | 1   | PWM circuit (Ch3) is selected.                                                             |

| 1   | 0   | 0   | PWM circuit (Ch4) is selected.                                                             |

| 1   | 0   | 1   | PWM circuit (Ch5) is selected.                                                             |

| 1   | 1   | 0   | PWM circuit (Ch6) is selected.                                                             |

| 1   | 1   | 1   | PWM circuit is not selected. (The setting of turning on/off of the duty 100% is possible.) |

<sup>11.</sup> LnC, LnB, LnA (n = 1 to 12) data are control data that set the Ch of PWM circuit for LED driver output pins LDn (n = 1 to 12). For example, if (L1C, L1B, L1A) = (0, 0, 1), (L5C, L5B, L5A) = (0, 1, 1) and (L10C, L10B, L10A) = (1, 1, 0) is set, LED driver output pin LD1 select PWM circuit (Ch1) and LED driver output pin LD5 select PWM circuit (Ch3) and LED driver output pin LD10 select PWM circuit (Ch6).

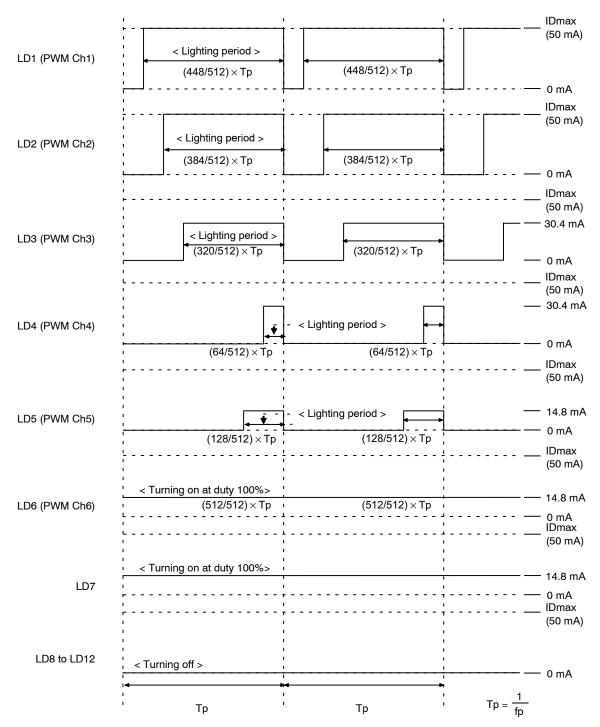

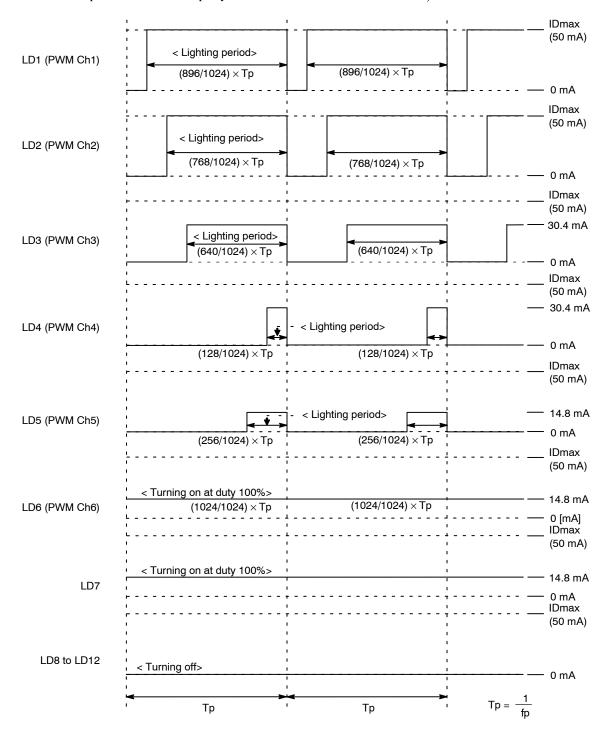

#### (3) WN1, WN0 • • • Control Data for Setting of the Resolution Number of PWM Steps of LED Driver Output Waveform

These control data bits set the steps number of PWM output (Ch1 to Ch6) of LED driver outputs (LD1 to LD12). In other word, they set the number of effective bits of PWM data. In addition, these control data are protected by the command [Lock of the PWM ch & PWM steps & PWM frame frequency]. It cannot change these control data when

the command [Lock of the PWM ch & PWM steps & PWM frame frequency] is set. When changing these control data, transmit the command [Unlock of the PWM ch & PWM steps & PWM frame frequency]. Afterwards set these control data. These control data are initialized to "(WN1, WN0) = (0,0)" by the reset action (reset by  $\overline{RES}$  pin, voltage detection type reset circuit (VDET), software reset or the thermal shut down actuating) of the system.

| WN1 | WNO | The Steps Number of PWM Output<br>(Ch1 to Ch6) of LED Driver Outputs LDn | The Number of Effective Bits of PWM Data per One Channel of PWM Data |

|-----|-----|--------------------------------------------------------------------------|----------------------------------------------------------------------|

| 0   | 0   | 128 steps                                                                | 7 bits (Wn9 to Wn3)                                                  |

| 0   | 1   | 256 steps                                                                | 8 bits (Wn9 to Wn2)                                                  |

| 1   | 0   | 512 steps                                                                | 9 bits (Wn9 to Wn1)                                                  |

| 1   | 1   | 1024 steps                                                               | 10 bits (Wn9 to Wn0)                                                 |

<sup>12.</sup> W19 to W10: PWM data of PWM circuit (Ch1) / W29 to W20: PWM data of PWM circuit (Ch2) W39 to W30: PWM data of PWM circuit (Ch3) / W49 to W40: PWM data of PWM circuit (Ch4) W59 to W50: PWM data of PWM circuit (Ch5) / W69 to W60: PWM data of PWM circuit (Ch6)

#### (4) PF3 to PF0 · · · Control Data for Setting of the Frame Frequency of PWM Output Waveform

These control data bits set the frame frequency of PWM output waveform of LED driver outputs (LD1 to LD12) setting PWM circuits (Ch1 to Ch6). In addition, these control data are protected by the command [Lock of the PWM ch & PWM steps & PWM frame frequency]. It cannot change these control data when the command [Lock of the

PWM ch & PWM steps & PWM frame frequency] is set. When changing these control data, transmit the command [Unlock of the PWM ch & PWM steps & PWM frame frequency]. Afterwards set these control data. These control data are initialized to "(PF3, PF2, PF1, PF0) = (1, 0, 0, 0)" all by the reset action (reset by  $\overline{RES}$  pin, voltage detection type reset circuit (VDET), software reset or the thermal shut down actuating) of the system.

|     |     |     |     |                                                            | WM Output Waveform<br>Outputs fp [Hz]                 |              | Number o     |              |               |

|-----|-----|-----|-----|------------------------------------------------------------|-------------------------------------------------------|--------------|--------------|--------------|---------------|

| PF3 | PF2 | PF1 | PF0 | Internal Oscillator Operating Mode (Control Data OC = "0") | External Clock Operating Mode (Control Data OC = "1") | 128<br>Steps | 256<br>Steps | 512<br>Steps | 1024<br>Steps |

| 0   | 0   | 0   | 0   | fosc / 2048                                                | f <sub>OSCI</sub> 1,2 / 2048                          | Υ            | Υ            | Υ            | Υ             |

| 0   | 0   | 0   | 1   | fosc / 1920                                                | f <sub>OSCI</sub> 1,2 / 1920                          | Υ            | N            | N            | N             |

| 0   | 0   | 1   | 0   | fosc / 1792                                                | f <sub>OSCI</sub> 1,2 / 1792                          | Υ            | Υ            | N            | N             |

| 0   | 0   | 1   | 1   | fosc / 1664                                                | f <sub>OSCI</sub> 1,2 / 1664                          | Υ            | N            | N            | N             |

| 0   | 1   | 0   | 0   | fosc / 1536                                                | f <sub>OSCI</sub> 1,2 / 1536                          | Υ            | Y            | Υ            | N             |