# Customer Demo Board for the WM7121P

#### **Features**

- WM7121P MEMS microphone

- Flexible PCB for full acoustic validation

- Pressure field

- Free field

- · Plug-and-play interface to smart codec main board

- Functional test

- Full signal path setup with smart codec

- System development and prototyping

- Algorithm verification

## **Description**

The CDB7121P is a flexible PCB for full electrical and acoustic validation of the WM7121P MEMS microphone. The CDB7121P is designed to connect to test equipment via on board test points or via a codec main board with mating edge connector socket.

The CDB7121P is ideally suited for pressure field acoustic measurements. Furthermore, the flexible region can be trimmed to enable accurate free field measurements to be made.

The CDB7121P also serves as a component and layout reference for the WM7121P.

## **Ordering Information**

CDBWM7121-M-2

Customer Demo Board

## **Table of Contents**

| 1 System Overview                | 3 |

|----------------------------------|---|

| 1.1 Test Points                  |   |

| 1.2 Edge Connector               |   |

| 1.3 Trim Line                    |   |

| 2 Quick Setup Guide              |   |

| 2.1 Pressure field acoustic test |   |

| 2.2 Free field acoustic test     |   |

| 3 Schematic                      |   |

| 4 Layout                         |   |

| 5 Known Issues                   |   |

| 6 Bill of Materials              | 7 |

| 7 Revision History               |   |

# 1 System Overview

The CDB7121P customer demo board is a flexible PCB for evaluating the WM7121P low-profile analog silicon microphone. The following subsections describe the features of CDB7121P customer demo board in detail.

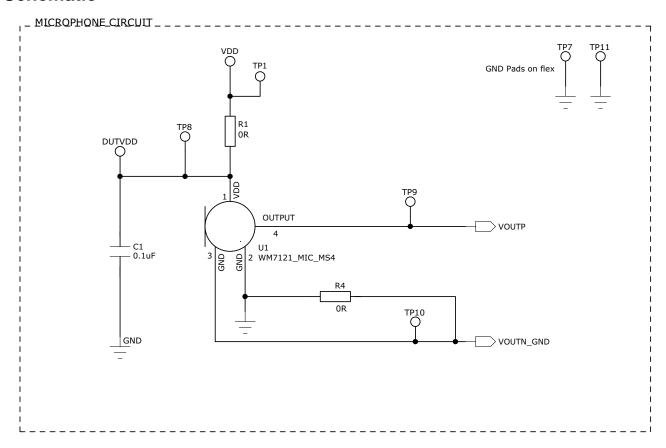

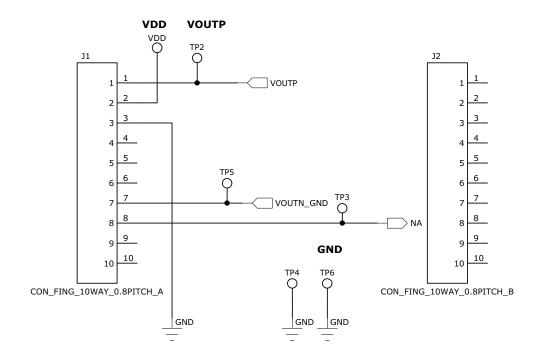

### 1.1 Test Points

Six test points are available to provide all the connections from WM7121P to standard test equipment for full acoustic measurement. Test points are described in Table 1-1. The operating supply voltage of WM7121P is provided in the data sheet, which is available from Cirrus website.

Table 1-1. Test Point signals

| Test Point    | Pin | Direction        | Description                       |

|---------------|-----|------------------|-----------------------------------|

| TP1           | VDD | Supply           | Analog Supply                     |

| TP2           | OP+ | Output           | Microphone analogue output signal |

| TP3           | NA  | NA               | Not Applicable                    |

| TP4, TP5, TP6 | GND | Ground reference | Analog Ground                     |

## 1.2 Edge Connector

The J1 and J2 edge connector pads provide a pluggable connection to a codec main board with compatible edge card socket. The edge connector pin-outs are described in Table 1-2 and Table 1-3.

Table 1-2. Edge connection J1

| Pin            | Pin | Direction        | Description                       |

|----------------|-----|------------------|-----------------------------------|

| 1              | OP+ | Output           | Microphone analogue output signal |

|                |     |                  | (pin 1 is marked by a small dot)  |

| 2              | VDD | Supply           | Analog supply from codec MICBIAS  |

| 3, 7           | GND | Ground reference | Analog ground                     |

| 8              | _   | _                | Not applicable                    |

| 4, 5, 6, 9, 10 | NC  | _                | No connection                     |

Table 1-3. Edge connection J2

| Pin                  | Pin | Direction | Description   |

|----------------------|-----|-----------|---------------|

| 1,2,3,4,5,6,7,8,9,10 | NC  | NA        | No Connection |

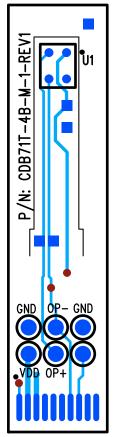

## 1.3 Trim Line

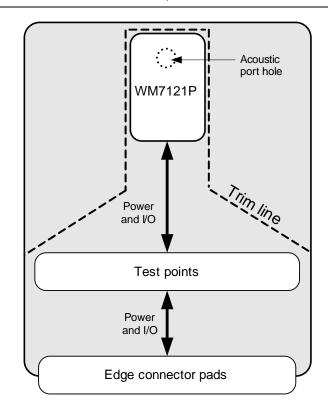

To enable more accurate free field frequency responses to be obtained, the flexible region of the CDB7121P may be trimmed to reduce acoustic interactions. If required, there is a guide line on the silkscreen that can be cut along. Refer to Fig. 4-1 for further details.

## 2 Quick Setup Guide

As a standalone PCB, the CDB7121P can be used in a pressure field acoustic test setup or free field acoustic test setup. It can also be connected to a compatible codec main board to enable full signal path setup within a system platform.

Acoustic measurements can be obtained using a number of different methods. Typical acoustic test setups, using a comparison method, are shown in Section 2.1 and Section 2.2.

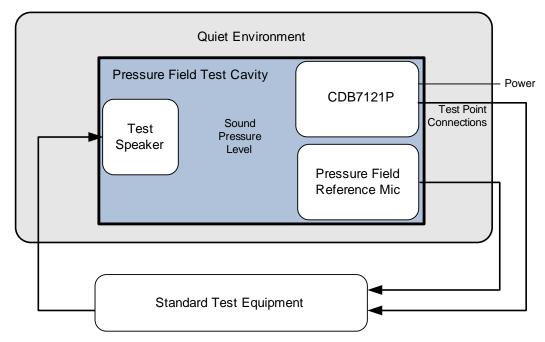

## 2.1 Pressure field acoustic test

Recommendations for accurate pressure field measurements are as follows:

- Ensure calibrated test equipment is used for making measurements

- Ensure CDB7121P acoustic port hole is tightly sealed within the pressure field test cavity

- Ensure CDB7121P and reference mic are placed close together with minimum placement error

- Use a suitable test microphone—a pressure field reference microphone is recommended

- Ensure the pressure field test cavity is tightly sealed

- Measurements should be performed within a quiet environment

Figure 2-1. Pressure field test setup with CDB7121P

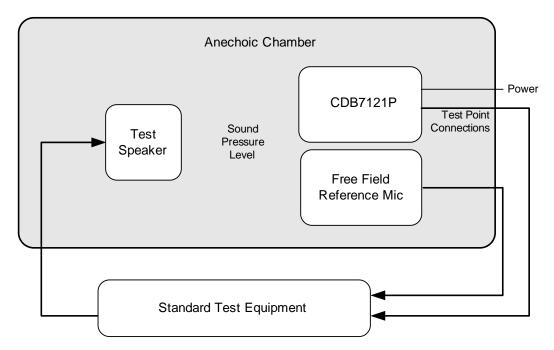

## 2.2 Free field acoustic test

Recommendations for accurate free field measurements are as follows:

- Ensure calibrated test equipment is used for making measurements

- Ensure CDB7121P acoustic port hole and reference mic are facing to the incoming sound pressure

- Ensure CDB7121P and reference mic are placed close together with minimum placement error

- The CDB7121P may be trimmed along the 'Trim line' to improve accuracy

- Use a suitable test microphone—a free field reference microphone is recommended

- Measurements should be performed within an anechoic environment

Figure 2-2. Free field test setup with CDB7121P

# 3 Schematic

# 4 Layout

Figure 4-1. Top Layer + Silkscreen

Figure 4-2. Bottom Layer + Silkscreen

# 5 Known Issues

There are no known issues with this board.

## 6 Bill of Materials

Table 6-1. Bill of Materials

| Item | em RefDes Description |                                               | Manufacturer | Manufacturer's Part Number |

|------|-----------------------|-----------------------------------------------|--------------|----------------------------|

| 1    | U1                    | WM7121P Bottom Port Analog Silicon Microphone | Cirrus Logic | WM7121PIMSE                |

| 2    | C1                    | 0.1-μF 0603 SMD Ceramic Capacitor 16 V X7R    | Phycomp      | 2238 786 15649             |

| 3, 4 | R1, R4                | 0-Ω 0603 SMD chip resistor 1% 0.063W          | Multicomp    | MC 0.063W 0603 0R          |

| 5    | PCB                   | WM7121P Top Port demo board PCB               | Cirrus Logic | CDB71T-4B-M1               |

# 7 Revision History

Table 7-1. Revision History

| Revision | Changes          |

|----------|------------------|

| DB1      | Initial version. |

| NOV '16  |                  |

**Important**: Please check www.Cirrus.com to confirm that you are using the latest revision of this document and to determine whether there are errata associated with this device.

### **Contacting Cirrus Logic Support**

For all product questions and inquiries, contact a Cirrus Logic Sales Representative. To find the one nearest you, go to www.cirrus.com.

#### IMPORTANT NOTICE

The products and services of Cirrus Logic International (UK) Limited; Cirrus Logic, Inc.; and other companies in the Cirrus Logic group (collectively either "Cirrus Logic" or "Cirrus") are sold subject to Cirrus Logic's terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, indemnification, and limitation of liability. Software is provided pursuant to applicable license terms. Cirrus Logic reserves the right to make changes to its products and specifications or to discontinue any product or service without notice. Customers should therefore obtain the latest version of relevant information from Cirrus Logic to verify that the information is current and complete. Testing and other quality control techniques are utilized to the extent Cirrus Logic deems necessary. Specific testing of all parameters of each device is not necessarily performed. In order to minimize risks associated with customer applications, the customer must use adequate design and operating safeguards to minimize inherent or procedural hazards. Cirrus Logic is not liable for applications assistance or customer product design. The customer is solely responsible for its selection and use of Cirrus Logic products. Use of Cirrus Logic products may entail a choice between many different modes of operation, some or all of which may require action by the user, and some or all of which may be optional. Nothing in these materials should be interpreted as instructions or suggestions to choose one mode over another. Likewise, description of a single mode should not be interpreted as a suggestion that other modes should not be used or that they would not be suitable for operation. Features and operations described herein are for illustrative purposes only.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). CIRRUS LOGIC PRODUCTS ARE NOT DESIGNED, AUTHORIZED OR WARRANTED FOR USE IN PRODUCTS SURGICALLY IMPLANTED INTO THE BODY, AUTOMOTIVE SAFETY OR SECURITY DEVICES, NUCLEAR SYSTEMS, LIFE SUPPORT PRODUCTS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF CIRRUS LOGIC PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK AND CIRRUS LOGIC DISCLAIMS AND MAKES NO WARRANTY, EXPRESS, STATUTORY OR IMPLIED, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR PARTICULAR PURPOSE, WITH REGARD TO ANY CIRRUS LOGIC PRODUCT THAT IS USED IN SUCH A MANNER. IF THE CUSTOMER OR CUSTOMER'S CUSTOMER USES OR PERMITS THE USE OF CIRRUS LOGIC PRODUCTS IN CRITICAL APPLICATIONS, CUSTOMER AGREES, BY SUCH USE, TO FULLY INDEMNIFY CIRRUS LOGIC, ITS OFFICERS, DIRECTORS, EMPLOYEES, DISTRIBUTORS AND OTHER AGENTS FROM ANY AND ALL LIABILITY, INCLUDING ATTORNEYS' FEES AND COSTS, THAT MAY RESULT FROM OR ARISE IN CONNECTION WITH THESE USES.

This document is the property of Cirrus Logic and by furnishing this information, Cirrus Logic grants no license, express or implied, under any patents, mask work rights, copyrights, trademarks, trade secrets or other intellectual property rights. Any provision or publication of any third party's products or services does not constitute Cirrus Logic's approval, license, warranty or endorsement thereof. Cirrus Logic gives consent for copies to be made of the information contained herein only for use within your organization with respect to Cirrus Logic integrated circuits or other products of Cirrus Logic, and only if the reproduction is without alteration and is accompanied by all associated copyright, proprietary and other notices and conditions (including this notice). This consent does not extend to other copying such as copying for general distribution, advertising or promotional purposes, or for creating any work for resale. This document and its information is provided "AS IS" without warranty of any kind (express or implied). All statutory warranties and conditions are excluded to the fullest extent possible. No responsibility is assumed by Cirrus Logic for the use of information herein, including use of this information as the basis for manufacture or sale of any items, or for infringement of patents or other rights of third parties. Cirrus Logic, Cirrus, the Cirrus Logic logo design, and SoundClear are among the trademarks of Cirrus Logic. Other brand and product names may be trademarks or service marks of their respective owners.

Copyright © 2016 Cirrus Logic, Inc. All rights reserved.